Custom AI acceleration continues to gather steam. In the cloud, Alibaba has launched its own custom accelerator, following Amazon and Google. Facebook is in the game too and Microsoft has a significant stake in Graphcore. Intel/Mobileye have a strong lock on edge AI in cars and wireless infrastructure builders are adding AI capabilities… Read More

Tag: calypto

HLS Rising

No-one could accuse Badru Agarwala, GM of the Mentor/Siemens Calypto Division, of being tentative about high-level synthesis. (HLS). Then again, he and a few others around the industry have been selling this story for quite a while, apparently to a small and not always attentive audience. But times seem to be changing. I’ve written… Read More

High Level Synthesis Update

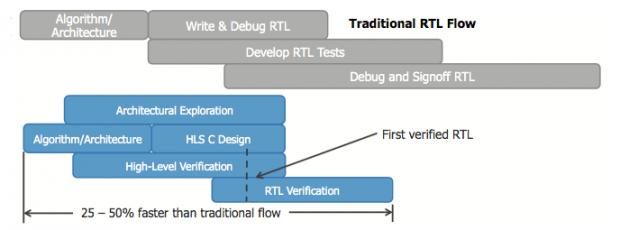

High-level synthesis (HLS) involves the generation of an RTL hardware model from a C/C++/SystemC description. The C code is typically referred to as abehavioraloralgorithmicmodel. The C language constructs and semantics available to architects enable efficient and concise coding – the code itself is smaller, easier to write/read,… Read More

Semiconductors Future Hinges on a Single Pillar

A unique phenomenon has started manifesting itself under the slew of mergers and acquisitions this year in the semiconductor landscape. This phenomenon is bound to intensify in the near future and would positions itself as a key factor for the future of the semiconductor industry. The winners and losers in the game would be determined… Read More

Leveraging HLS/HLV Flow for ASIC Design Productivity

Imagine how semiconductor design sizes leapt higher with automation in digital design, which started from standard hardware languages like Verilog and VHDL; analog design automation is still catching up. However, it was not without a significant effort put in moving designers from entering schematics to writing RTL, which… Read More

Nine Cost Considerations to Keep IP Relevant

It’s about 15 years the concept of IP development and its usage took place. In the recent past the semiconductor industry witnessed start of a large number of IP companies across the globe. However, according to Gary Smith’s presentation before the start of 52[SUP]nd[/SUP] DAC, IP business is expected to remain stagnant for next… Read More

Designing an IDCT for H.265 using High Level Synthesis

Math geeks know all about Inverse Discrete Cosine Transforms (IDCT) and a popular use is in the hardware architecture of High Efficiency Video Coding (HEVC), also known as H.265, the new video compression standard and widely used in consumer and industrial video devices. You could go about hand-coding RTL to create an IDCT function,… Read More

Choosing C++ or SystemC for High Level Synthesis

Most engineers learn by doing, and so at DAC in June an EDA vendor with High Level Synthesis (HLS) tools held a language tutorial on choosing C++ or SystemC for design and verification projects. The EDA company is Calypto, and Stuart Clubb put together the tutorial on using synthesizable C++ or SystemC. The design and verification… Read More

High Level Synthesis. Are We There Yet?

High level synthesis (HLS) seems to have been part of the backdrop of design automation for so long that it seems to be one of those things that nobody notices any more. But it has also crept up on people and gone from interesting technology to keep an eye on to getting genuine adoption. The first commercial product in the space was behavioral… Read More

NVIDIA and Qualcomm Talk about High Level Synthesis, Samsung on Low Power for Mobile

Since 1978 I’ve seen many trends in the semiconductor design world: transistor-level IC design, gate-level design, RTL coding, High Level Synthesis (HLS) and IP re-use. We’ve witnessed the growth in design productivity enabling chips starting with just thousands of transistor all the way up to billions of transistors… Read More