Custom and analog/mixed-signal IC designs have some unique IP and symmetry checking requirements for physical design. Waiting until the end of the IC layout process to verify IP instances for correctness or proper symmetry will cause project delays, so an approach to perform earlier physical verification makes more sense. … Read More

Tag: calibre realtime

What’s New With Calibre at DAC This Year?

When I worked at EDA vendors and attended DAC, one of the most popular questions asked in the booth and suites was simply, “What’s new this year?” It’s a fair question, and yet many semiconductor professionals are so focused on their present project, using their familiar methodology, that they simply… Read More

Mentor at the 55th Design Automation Conference

It’s hard to believe that this is the 55th DAC and even harder to believe that this will be my 35th. So much has changed in 35 years, with DAC back in San Francisco I expect a VERY big crowd and even bigger announcements, absolutely.

Not only is this an epic time for semiconductors, I would say that EDA is exciting again and the Mentor… Read More

Top 10 Reasons to invest in Interactive Design Rule Checking tools

One of the most energetic presentations at the recent TSMC OIP 2015 symposium was given by Tom Williams from Qualcomm, who shared his insights (and enthusiasm!) for Mentor’s Calibre RealTime interactive Design Rule Checking (iDRC) product.

Paraphrasing Tom’s presentation (and with a tip of the hat to David Letterman), here … Read More

Diagnosing Double Patterning Violations

I’ll bet you’ve read a bunch of stuff about double patterning, and you’re probably hoping that the design tools will make all your double patterning issues just go away. Well, the truth is that the foundries and EDA vendors have worked really hard to make that true.

However, for some critical portions of your design, there … Read More

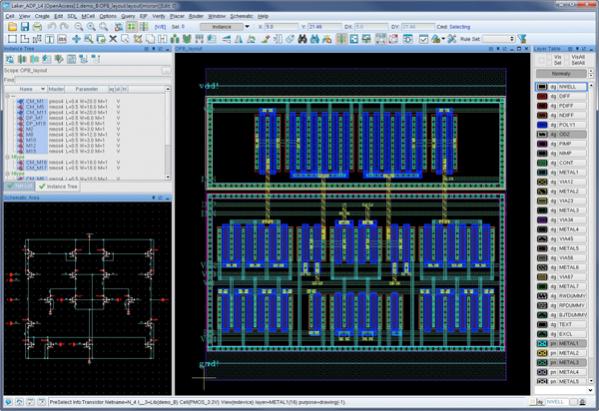

Laker Wobegon, where all the layout is above average

TSMC’s technnology symposium seems to be the new time to make product announcements, with ARM and Atrenta yesterday and Springsoft today.

There is a new incarnation of Springsoft’s Laker layout family, Laker[SUP]3[/SUP] (pronounced three, not cubed). The original version ran on its own proprietary database.… Read More