I wrote a while back about some of the more exotic architectures for machine learning (ML), especially for neural net (NN) training in the data center but also in some edge applications. In less hairy applications, we’re used to seeing CPU-based NNs at the low end, GPUs most commonly (and most widely known) in data centers as the workhorse… Read More

Tag: cache

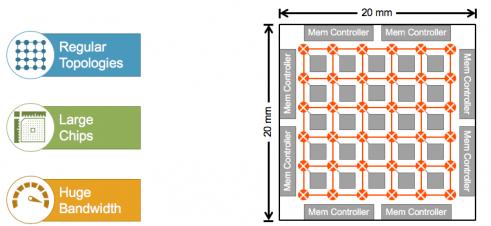

A Last-Level Cache for SoCs

We tend to think of cache primarily as an adjunct to processors to improve performance. Reading and writing main memory (DRAM) is very slow thanks to all the package and board impedance between chips. If you can fetch blocks of contiguous memory from the DRAM to a local on-chip memory, locality of reference in most code ensures much… Read More

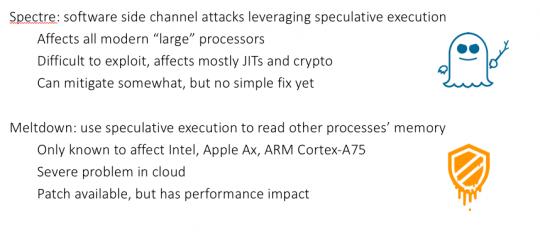

Meltdown, Spectre and Formal

Once again Oski delivered in their most recent Decoding Formal session, kicking off with a talk on the infamous Meltdown and Spectre bugs and possible relevance of formal methods in finding these and related problems. So far I haven’t invested much effort in understanding these beyond a hand-waving “cache and speculative execution”… Read More

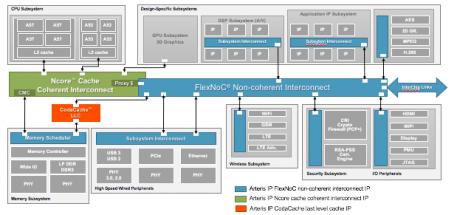

Arteris Unveils Solution for Heterogeneous Cache Coherent SOC’s

Designing SOC’s for markets like automotive and mobile electronics requires taking advantage of every opportunity for optimization. One way to do this is through building a cache coherent system to boost speed and reduce power. Recently, NXP decided to go about this on their automotive MCU based SOC’s by using Arteris’ just-announced… Read More

Cortex-M7: 6-stage, cached, 400 MHz MCU

“Who needs a 32-bit MCU?” It was a question asked a million times in the press when ARM introduced the Cortex-M family back in 2004. In fairness, that question predates the Internet of Things, with wireless sensor networks, open source code, encryption, and more needs for connected devices.… Read More

Learning Cache Coherency and Cache Coherent Interconnects: ARM White Paper

Cache Coherency is the type of concept that you think you understand, until you try to explain it. It could be wise to come back to fundamentals, and ask what does coherency means to an expert. I have surf the web, found several white papers on ARM site, and now I can try to share these fresh lessons learned (or you may prefer to download… Read More

Cache Coherency and Verification Seminar

At DAC Jasper presented a seminar with ARM on cache coherency and verification of cache coherency. The seminar is now available online for those of you that missed DAC or missed the seminar itself.

Cache architectures, especially for multi-core architectures, are getting more and more complex. Techniques originally pioneered… Read More