According to the IEEE Std 1012-2012, verification is the acknowledgement that a product is in satisfactory condition by meeting a set of rigorous criteria. [3] Transistor-level verification involves the use of custom libraries and design models to achieve ultimate performance, low power, or layout density. [2] Prediction… Read More

Tag: bti

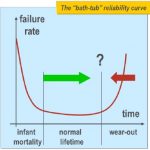

Predicting Lifetime of Analog ICs

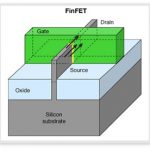

With the increase of transistors per unit area, high density interconnects and manufacturing variability at lower nodes, the electronic devices have become more vulnerable to failures. The devices that operate under extreme conditions such as automotive devices that operate at high temperatures need to be robust enough to… Read More

UTBB FDSOI Devices Featuring 20nm Gate Length

Did you go to IEDM 2013 in Washington DC ? You may have attended to the “Advanced CMOS Technology Platform” chaired by TSMC, and listen to the FD-SOI related presentation “High Performance UTBB FDSOI Devices Featuring 20nm Gate Length for 14nm Node and Beyond”. According with the abstract, this paper is the first time report of “high… Read More