You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

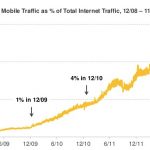

Mobile devices are taking over the world. If you want lots of graphs and data then look at Mary Meeker’s presentation that I blogged about earlier this week. The graph on the right is just one datapoint, showing that mobile access to the internet is probably up to about 15% now from a standing start 5 years ago.

Of course, one obvious… Read More

Watch the Clockby Paul McLellan on 03-05-2013 at 2:24 pmCategories: Ansys, Inc., EDA

Clock gating is one of the most basic weapons in the armoury for reducing dynamic power on a design. All modern synthesis tools can insert clock gating cells to shut down clocking to registers when the contents of the register are not changing. The archetypal case is a register which sometimes loads a new value (when an enable signal… Read More

DesignConis next week in Santa Clara, so today I spoke with Mark Ravenstahlfrom ANSYS to get an idea of what to expect at the conference and trade show.

… Read More

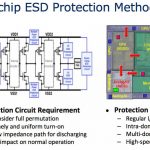

In Pune at the start of the month, Norman Chang, Ting-Sheng Ku, Jai Pollayil of Apache/Ansys and NVIDIA presented and ESD check methodologywith Fast Full-chip Static and Macro-level Dynamic Solutions . ESD stands for Elecro-Static Discharge and is basically injecting very high static voltages (think how your hand gets charged… Read More

Late in January it is DesignCon at the Santa Clara convention center from January 28th-31st. Details are here.

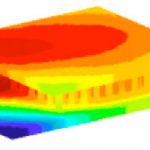

On Tuesday from 11.05 to 11.45 Apache and Ansys will be presenting on Thermal Co-analysis of 3D IC/packages/system. This is being presented by a whole team of people: Stephen Pan, senior product specialist at ANSYS; Norman… Read More

The 26th Conference on VLSI Design will be in Pune, India from January 5th to 10th at the Hyatt Regency. Details on the conference here. Registration here. I happened to be involved in the first of these conferences, which was held in Edinburgh where I was wrapping up my PhD. It was in the considerably less palatial surroundings of … Read More

This is the second part of my discussion with Paul Traynar, Apache’s PowerArtist guru. The first part discussed sequential reduction capabilities. Part I was here.

There are two big challenges with doing power analysis at the RTL level. Firstly, how do you get an accurate enough model of what the design will dissipate given… Read More

I sat down last week with Paul Traynar who was over from UK. He is Apache’s PowerArtist guru. The first thing we talked about was PowerArtist’s sequential power reduction capabilities.

Forward propagation of enables means that when a register is clock gated and feeds a downstream register then that register can be… Read More

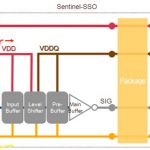

Matt Elmore has a two-part blog about the growing complexity of signal integrity analysis, both on the chip itself and the increasingly complex analysis required to make sure that signals (and power) get in and out of the chip from the board cleanly, especially to memory, which requires simultaneous analysis of chip-package-system… Read More

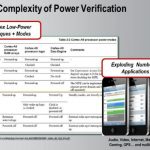

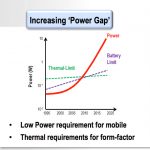

Last week I attended the Ansys/Apache seminars on “Dimensions of Electronic Design.” The two big challenges as we go down to 28nm and 20nm and below are keeping power manageable and keeping reliability up.

The big challenge with power is that we can put so much stuff on a die and clock it so fast that the power is exceeding… Read More