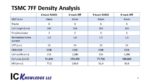

I have written a lot of articles looking at leading edge processes and comparing the process density. One comment I often get are that the process density numbers I present do not correlate with the actual transistor density on released products. A lot of people want to draw conclusions an Intel’s processes versus TSMC’s processes… Read More

Tag: 7ff

TSMC Teamwork Translates to Technical Triumph

Most people think that designing successful high speed analog circuits requires a mixture of magic, skill and lots of hard work. While this might be true, in reality it also requires a large dose of collaboration among each of the members of the design, tool and fabrication panoply. This point was recently made abundantly clear … Read More

Xilinx Skips 10nm

At TSMC’s OIP Symposium recently, Xilinx announced that they would not be building products at the 10nm node. I say “announced” since I was hearing it for the first time, but maybe I just missed it before. Xilinx would go straight from the 16FF+ arrays that they have announced but not started shipping, and to the… Read More