NVIDIA designs some of the most complex chips for GPU and AI applications these days, with SoCs exceeding 21 billion transistors. They certainly know how to push the limits of all EDA tools, and they have a strong motivation to automate more manual tasks in order to quicken their time to market. I missed their Designer/IP Track Poster… Read More

Tag: #56dac

#DAC56 – Optimizing Verification Throughput for Advanced Designs in a Connected World

It was the final day of DAC56 and my head was already spinning from information overload after meeting so many people and hearing so many presentations, but I knew that IC functional verification was a huge topic and looming bottleneck for many SoC design teams, so I made a last-minute email request to attend a luncheon panel discussion… Read More

#56DAC Update – What’s New at Concept Engineering

I first connected with Gerhard Angst of Concept Engineering over 15 years ago, because I was using their SpiceVision PRO tool to visual SPICE netlists received from customer designs to be debugged in a FastSPICE circuit simulator. The ability to visualize a transistor-level netlist was simply essential to quickly understanding… Read More

#56DAC – Functional Safety Panel hosted by Mentor

Four experts in the discipline of functional safety were gathered together at #56DAC in Vegas earlier in June, hosted at the Mentor booth, so I rested my legs and typed notes as fast as I could. The product areas that I first think about when functional safety (FuSa) comes up are automotive, medical and aerospace, because keeping… Read More

#56DAC – What’s New with Custom Design Platform

TSMC attends DAC every year and they do something very savvy, it’s a theatre where they invite all of their EDA and IP partners to present something of interest, followed by a drawing for a prize. At the end of the day they even have a nice prize, like a MacBook Air, which I didn’t win. On Wednesday I watched Dave Reed of Synopsys… Read More

#56DAC – Panel Discussion: Closing Analog and Mixed-Signal Verification in 5G, HPC and Automotive

Monday afternoon at #56DAC I enjoyed attending a luncheon panel discussion from four AMS experts and moderator, Prof. Georges Gielen, KU Leuven. I follow all things SPICE and this seemed like a great place to get a front-row seat about the challenges that only a SPICE circuit simulator can address. Here’s a brief introduction… Read More

Needham is Upbeat about EDA and IP Growth at #56DAC

It’s Sunday afternoon and I just attended the annual Needham presentation at #56DAC in sunny Las Vegas, where Rich Valera shared an upbeat view of EDA and IP growth. Here are the five drivers of this growth:

- IoT

- Automotive

- Webscale/FAANGs

- AI/ML

- China

For the IoT market they’ve seen a CAGR of 8.6% to $8.2B in 2018, projected… Read More

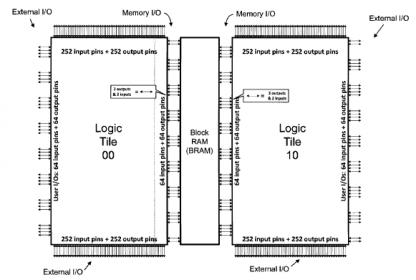

Block RAM integration for an Embedded FPGA

The upcoming Design Automation Conference in San Francisco includes a very interesting session –“Has the Time for Embedded FPGA Come at Last?” Periodically, I’ve been having coffee with the team at Flex Logix, to get their perspective on this very question – specifically, to learn about the key features that customers are seeking… Read More