This will probably end up being the most memorable DAC for us since Paul and I signed hundreds of copies of our book “Fabless: The Transformation of the Semiconductor Industry”. I’m not sure how we are going to top that next year but I’m confident we will think of something. If you want to catch up on the live blogs from the last three conferences… Read More

Tag: #51dac

RTL Signoff Update from #51DAC

In the early days of Customer Owned Tooling (COT) the signoff was done at the GDS II, or physical level. Today, however we see the trend of RTL signoff instead because of the EDA tools and methodology available. At DACearlier this month I met with Piyush Sanchetiof Atrenta to get an update on what’s new with RTL signoff.… Read More

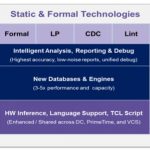

Synopsys Revamps Formal at #51DAC

Synopsys announced verification compiler a couple of months ago and dropped hints about their static and formal verification. They haven’t announced anything much for a couple of years and it turns out that the reason was that they decided that the technology that they had, some internally developed and some acquired, … Read More

Virtual Prototype Update from #51DAC

EDA industry pundit Gary Smithhas been talking about the electronics industry adopting an ESL tool flow for decades, so it was my pleasure to speak with Bill Neifertof Carbon Design Systemsat DAC this month because his company has been offering both tools and models that enable a virtual prototyping design flow.… Read More

High Level Synthesis update from #51DAC

Every since Synopsys dominated the logic synthesis market in the 1980’s we’ve had something called HLS – High Level Synthesis, meaning something higher than what Design Compiler can understand as input. At DACthis year I met with Mark Milligan of Calypto to get an update on what’s new with HLS. I first… Read More

Standard Cell, IO and Hard IP Validation update

Every SoC team uses libraries of cells to get their new product to market quicker: Standard Cells, IO Cells and Hard IP blocks. One immediate question that comes to my mind is, “How clean are these cells?” Validating your cell libraries first makes sense, and will ensure that there are fewer surprises as your chip gets… Read More

IP Management Update at DAC

To keep track of my business and personal finances I use software from Quicken, but for an SoC with hundreds of IP blocks how do you keep track of everything? The answer is found in the growing field of EDA tools for IP management, and at DACearlier this month I sat down with Neil Handof Methodics to get an update on what the industry trends… Read More

What’s New with Circuit Simulation for Cadence?

Every year at DAC I enjoy making the rounds to see what’s new with SPICE circuit simulators, so on June 3rd I met with Xiuya Liand Dan Zhuof Cadence in San Francisco to get an update about their Spectre tool. There’s plenty of competition in the SPICE area from Mentor Graphics (Analog FastSPICE, Eldo, ADiT), Synopsys … Read More

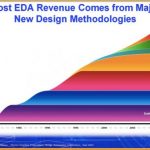

Wally Rhines at #51DAC: EDA Grows From Solving New Problems

Wally Rhines gave the keynote at DAC in 2004. One of the things that he pointed out ten years ago was that EDA revenue for any given market segment is pretty much flat once the initial growth phase has taken place and the market has been established. Incremental EDA revenue only comes from delivering new capabilities. Historically… Read More

ESL Tool Update from #51DAC

As promised in my May 27th blog, I visited an ESL company at DAC three weeks ago that introduced two new tools:

- Thermal Profiler

- Power Intelligence