Design IP is going well, with 12% YoY growth in 2017, even if the market is about $3.5B. But Design IP is serving a $400B semiconductor market. Can you imagine the future of the semi market if the chip makers couldn’t have access to Design IP? The same is true for EDA: it’s a niche market (CAE revenues was about $3B and IC Physical Design & Verification revenue was less than $2B in 2017) driving a $400B market!

We will concentrate on IP, as I am proudly part of the DAC IP Committee since 2016, and I would like to highlight some session during next DAC in San Francisco, including the two I am chairing.

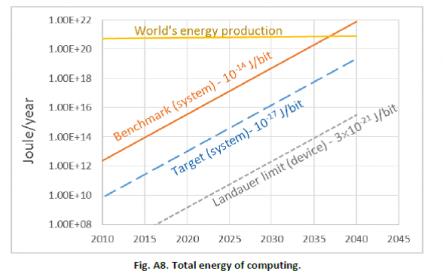

I will certainly attend on Monday 25[SUP]th[/SUP] to this session “Minimizing IC Power Consumption with PPA Optimized IPs” chaired by Farzad Zarrinfar and moderated by John Blyler. Not only because Frederic Renoux, VP sales for Dolphin Integration will be one of the panelist (Dolphin is one of my rare customer to be located in France), with Lluis Paris from TSMC (another IPnest customer…), but because I strongly think that low power will be key in the near future. Let’s call it “Energy Efficiency” instead of just low power and look at the above picture: if SoC design stay as it is today, the total energy of computing will consume more than the world’s energy production in 2040!

We have been used to a communication only focused on SoC performance (like with Intel CPU, the only metric was x.y GHz), but the chip makers will have to invest into energy efficient chips development, as their customers (running data center or simply integrating IoT devices in their systems) will force them to provide better chips, energy efficient chips.

I will have no other choice than attending on Tuesday 26[SUP]th[/SUP] at 10:30 the invited session “IP and Architectures for CMOS Imager Sensors”, as I am the chairman! Moreover, I have suggested the topic to the Committee, as CIS is already a very healthy segment of the semi market, weighting $12B in 2017 according with YOLE. The CIS market has exploded to bring always more performant CMOS Imagerto the mobile phone industry where the camera is becoming the Top selling argument (you don’t sell a smartphone because it integrates the best Viterbi algorithm).

And the CIS market is expected to rebound, thanks to the automotive segment where mirrors will be replaced by camera (today) and when many cameras, radars, LIDAR will be integrated to support autonomous vehicle (tomorrow). I am sure that most of the readers don’t know about CIS architecture, and about the type of IP integrated into a CIS (just like me in January 2017 when I started to work on this technology). I can tell you, it’s fascinating! Plenty of innovation are needed, the designers play at the limits of physical science. You will certainly learn a lot and learn from the best WW experts like Jean-Luc Jaffard, CIS market veteran working for Prophesee , who will give a state of the art overview to introduce the topic.

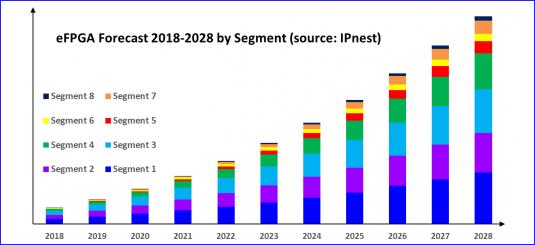

Still on Tuesday 26[SUP]th[/SUP], at 1:30 pm, I will not miss this session “Has The Time For Embedded FPGA Come At Last?” chaired by Ty Garibay, the DAC IP Committee chairman, CTO of Arteris, after working Intel, Altera and TI! IPnest has released a report in April this year “eFPGA IP Market Survey & Forecast-2018-2028” showing that, if the industry confirms the adoption trend for embedded FPGA, this IP market should explode and pass the $1 billion in 10 years. The “usual suspects” are part of this session with presentation from Steve Mensor (Achronix), Cheng Wang (Flex Logix) presenting with John Teifel (Sandia National Laboratories) as eFPGA IP customer and Yoan Dupret (Menta). I say usual suspects as all of them are active in communication since a couple of years, including blogs in Semiwiki, with maybe a special mention to Flex Logix in term of marcom activity! Just a precision: to be selected to present in this session, one important criteria was to justify having a SoC customer, in production. All of them have at least one identified customer (and they can share the name).

There are plenty of other session I recommend attending, including “New Challenges for IP and VIP to Support Emerging Application or Algorithm” still on Tuesday 26[SUP]th[/SUP] , at 3:30 pm, that I am chairing too, with 6 submitted papers.

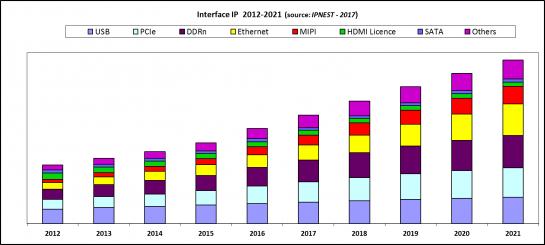

Or “Latest Developments in High Performance SoC Interface IP Standards” an invited session chaired by Chirag Dhruv (AMD), dealing with IPnest domain of expertise, Interface IP (see the market report and forecast on the above picture), but it’s difficult to name all the IP sessions. But I can guarantee that the quality of the papers, submitted or invited is excellent (foar having spent hours to review and select it)!

You should go on: DAC 2018 IP & Design and also select the topic which best fit your interest.

Eric Esteve from IPnest

Share this post via:

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center