In his keynote at the TSMC OIP Ecosystem Forum Dr. LC Lu, TSMC Senior Fellow and Vice President, Research & Development / Design & Technology Platform, highlighted the exponential rise in power demand driven by AI proliferation. AI is embedding itself everywhere, from hyperscale data centers to edge devices, fueling new applications in daily life.

Evolving models, including embodied AI, chain-of-thought reasoning, and agentic systems, demand larger datasets, more complex computations, and extended processing times. This surge has led to AI accelerators consuming 3x more power per package in five years, with deployments scaling 8x in three years, making energy efficiency paramount for sustainable AI growth.

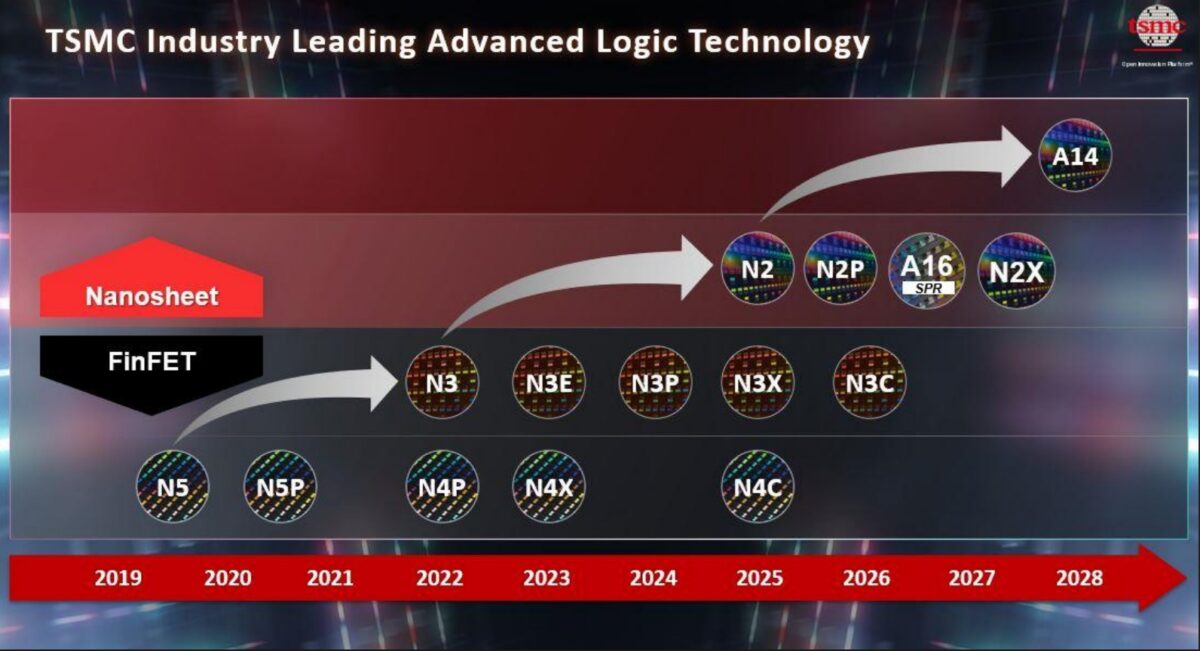

TSMC’s strategy focuses on advanced logic and 3D packaging innovations, coupled with ecosystem collaborations, to tackle this challenge. Starting with logic scaling, TSMC’s roadmap is robust: N2 will enter volume production in the second half of 2025, N2P slated for next year, A16 with backside power delivery by late 2026, and A14 progressing smoothly.

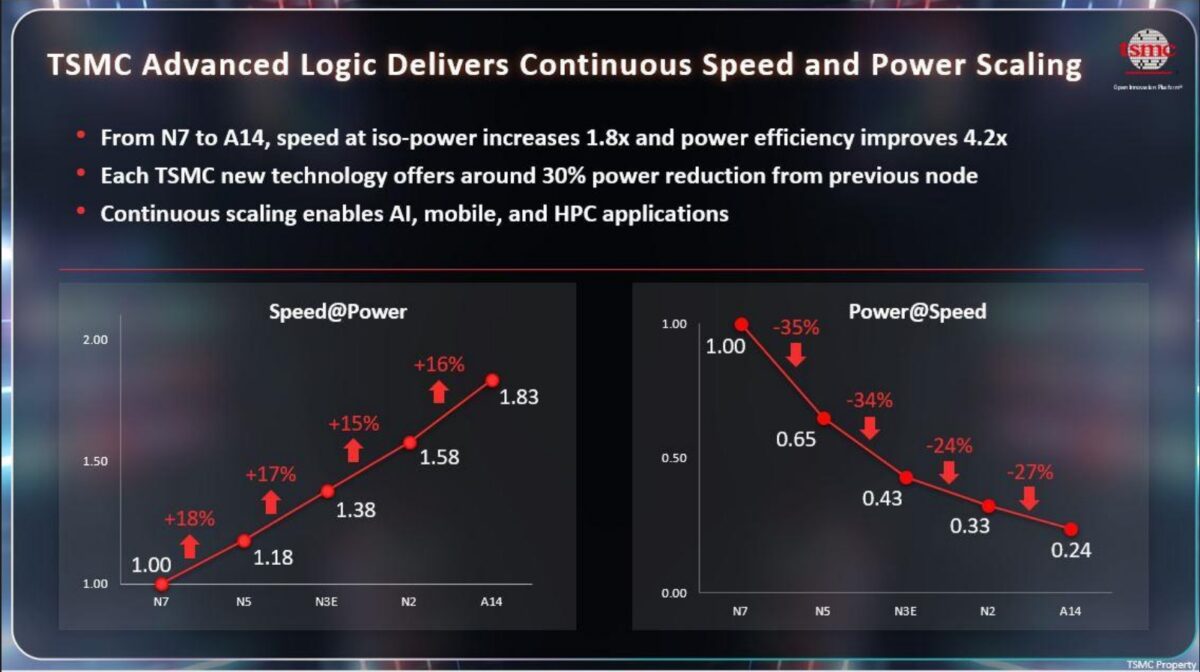

Enhancements to N3 and N5 continue to add value. From N7 to A14, speed at iso-power rises 1.8x, while power efficiency improves 4.2x, with each node offering about 30% power reduction over its predecessor. A16’s backside power targets AI and HPC chips with dense networks, yielding 8-10% speed gains or 15-20% power savings versus N2P.

N2 Nanoflex DTCO optimizes designs for dual high-speed and low-power cells, achieving 15% speed boosts or 25-30% power reductions. Foundation IP innovations further enhance efficiency. Optimized transmission gate flip-flops cut power by 10% with minimal speed (2%) and area (6%) trade-offs, sometimes outperforming state gate variants.

Dual-rail SRAM with turbo/nominal modes delivers 10% higher efficiency and 150mV lower Vmin, with area penalties optimized away. Compute-In-Memory stands out: TSMC’s digital CIM based Deep Learning Accelerator offers 4.5x TOPS/W and 7.8x TOPS/mm² over traditional 4nm DLAs, scaling from 22nm to 3nm and beyond. TSMC invites partnerships for further CIM advancements.

AI-driven design tools amplify these gains. Synopsys’ DSO.AI is the leader with reinforcement learning for PPA optimization, improving power efficiency by 5% in APR flows and 2% in metal stacks, totaling 7%. For analog designs integrations with TSMC APIs yield 20% efficiency boosts and denser layouts. AI assistants accelerate analysis 5-10x via natural language queries for power distribution insights.

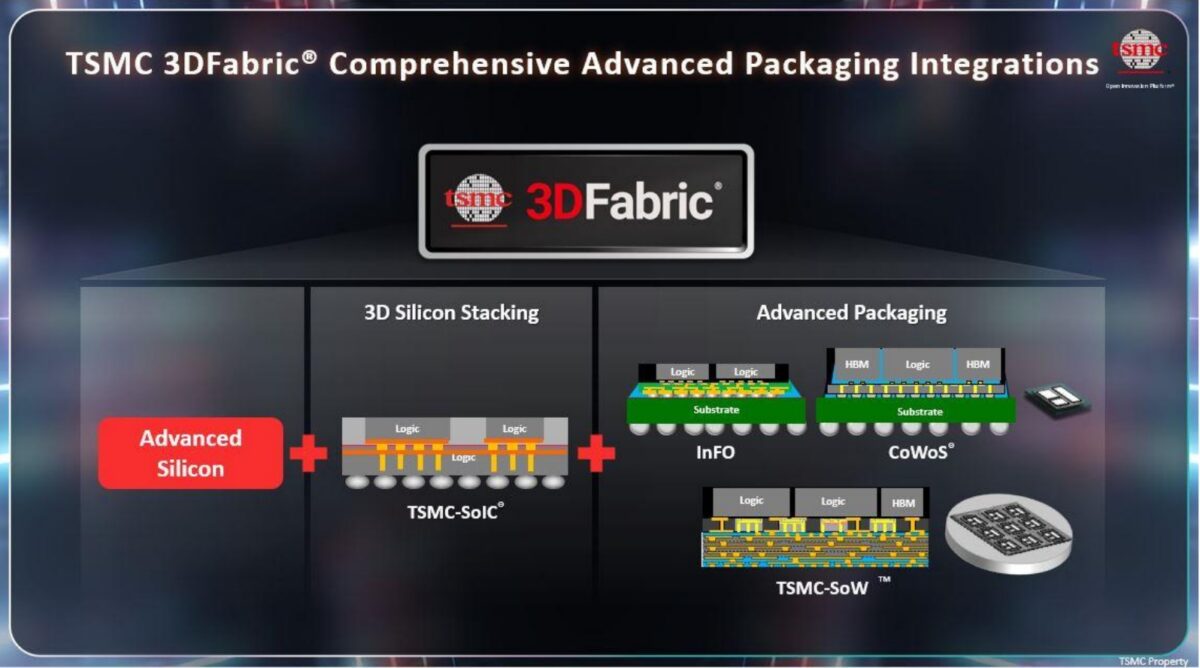

Shifting to 3D packaging, TSMC’s 3D Fabric includes SoIC for silicon stacking, InFO for mobile/HPC chiplets, CoWoS for logic-HBM integration, and SoW for wafer-scale AI systems. Energy-efficient communication sees 2.5D CoWoS improving 1.6x with microbump pitches from 45µm to 25µm. 3D SoIC boosts efficiency 6.7x over 2.5D, though with smaller integration areas (1x reticle vs. 9.5x). Die-to-die IPs, aligned with UCIE standards, are available from partners like AlphaWave and Synopsys.

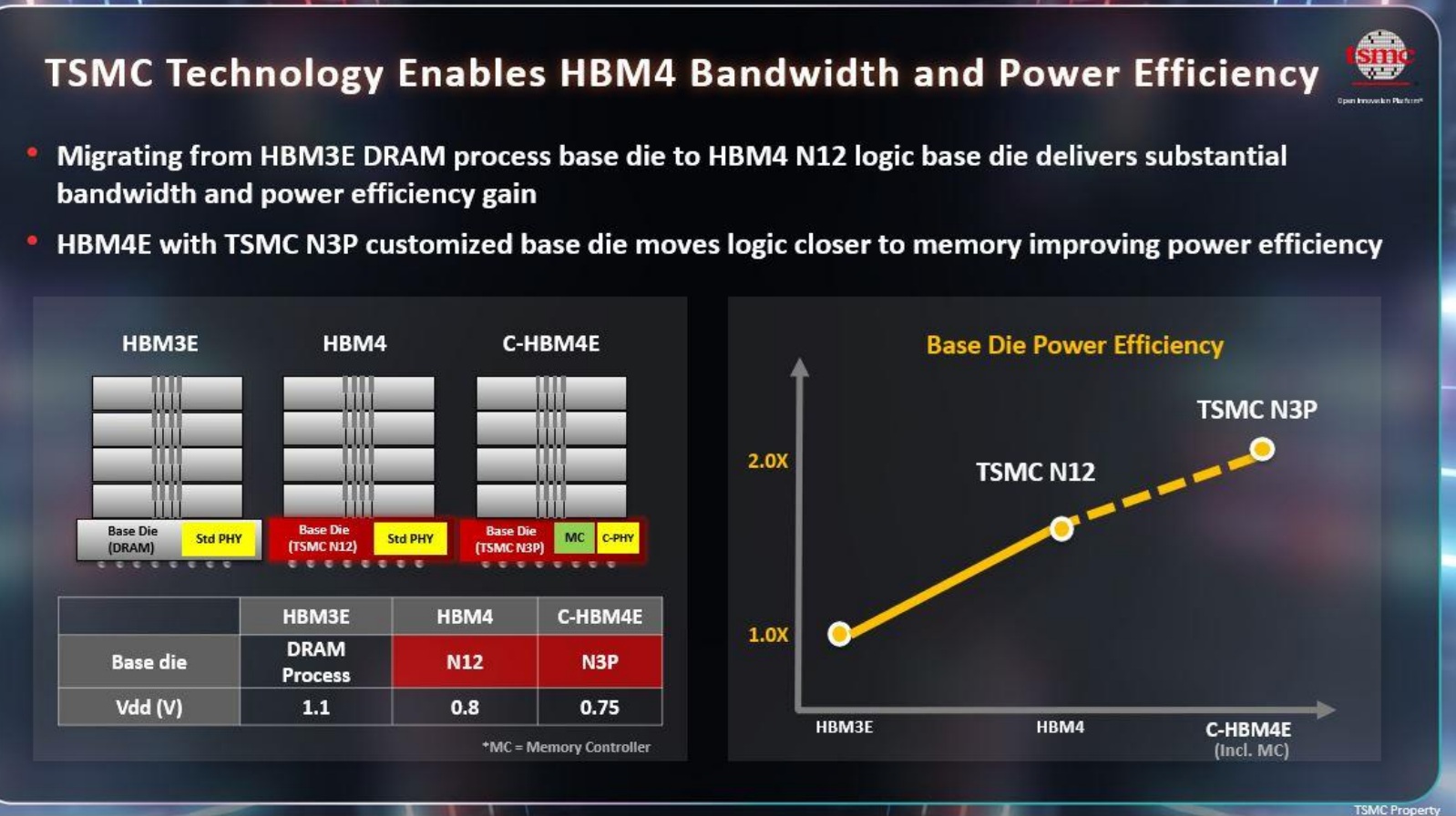

HBM integration advances: HBM4 on TSMC’s N12 logic base die provides 1.5x bandwidth and efficiency over HBM3e DRAM dies. N3P custom bases reduce voltage from 1.1V to 0.75V. Silicon photonics via co-packaged optics offers 5-10x efficiency, 10-20x lower latency, and compact forms versus pluggables. AI optimizations from Synopsys/ANSYS enhance this by 1.2x through co-design.

Decoupling capacitance innovations using Ultra High-Performance Metal-Insulator-Metal plus Embedded Deep Trench Capacitor enables 1.5x power density without integrity loss, modeled by Synopsys/ANSYS tools. EDA-AI automates EDTC insertion (10x productivity) and substrate routing (100x, with optimal signal integrity).

![]()

Bottom line: Moore’s Law is alive and well. Logic scaling delivers 4.2x efficiency from N7 to A14, CIM adds 4.5x IP/design innovations contribute 7-20%. Packaging yields 6.7x from 2.5D to 3D, 5-10x from photonics, and 1.5-2x from HBM/ Decoupling Capacitor advances, with AI boosting productivity 10-100x.

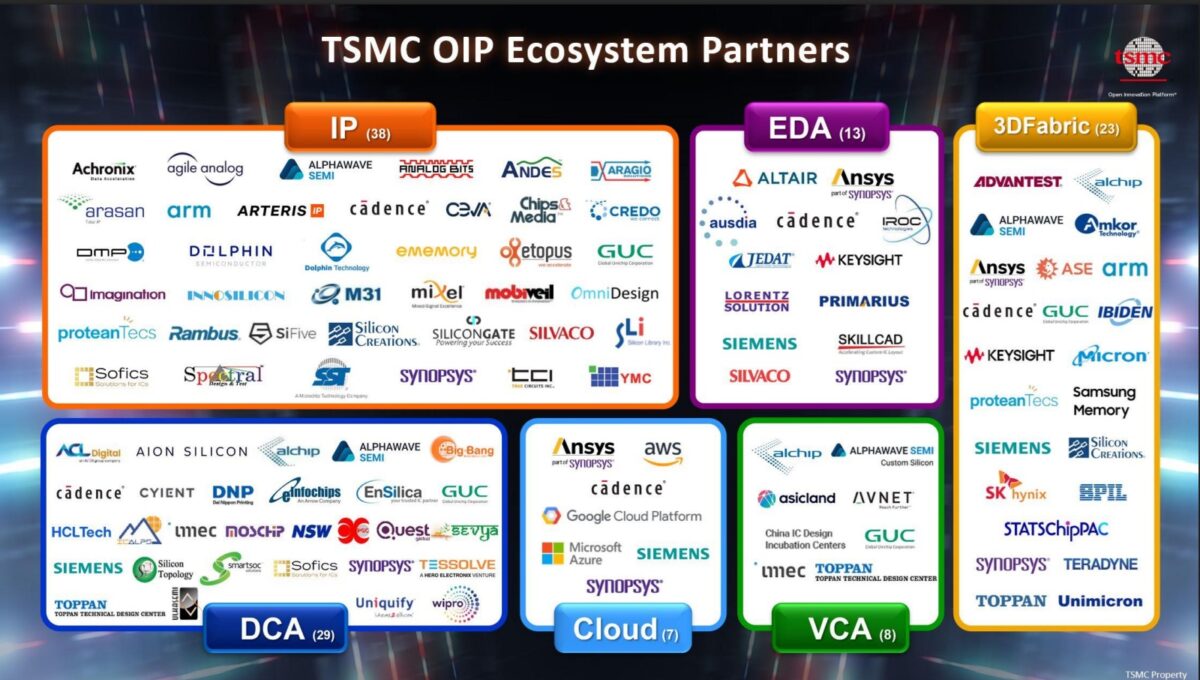

TSMC honored partners with the 2025 OIP Awards for contributions in A14/A16 infrastructure, multi-die solutions, AI design, RF migration, IP, 3D Fabric, and cloud services. It is all about the ecosystem, absolutely.

Exponential AI power needs demand such innovations. TSMC’s collaborations drive 5-10x gains fostering efficient, productive AI ecosystems. Looking ahead, deeper partnerships will unlock even more iterations for sustainable AI advancement.

Also Read:

TSMC’s 2024 Sustainability Report: Pioneering a Greener Semiconductor Future

TSMC 2025 Update: Riding the AI Wave Amid Global Expansion

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.