I’m looking forward to the 2013 TSMC Open Innovation Platform Ecosystem Forum to be held Oct. 1[SUP]st[/SUP] in San Jose. One paper in particular that has my attention is titled, “An Efficient and Accurate Sign-Off Simulation Methodology for High-Performance CMOS Image Sensors,” by Berkeley Design Automation & Forza Silicon. It is not every day that we get a chance to learn how design teams are tackling the tough verification challenges in complex high-performance applications, such as image sensors.

CMOS Image Sensor

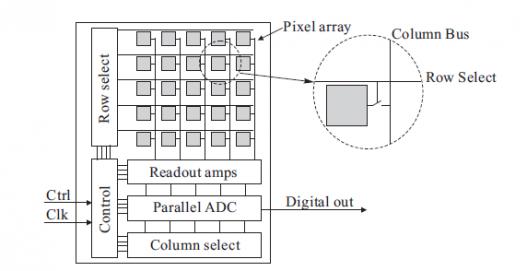

The paper will discuss how many image sensor performance-limiting factors appear only when all of the active and passive devices in the array are modeled, including random device noise and layout parasitics. Coupled with the highly sensitive nature of image sensors, where tens of microvolts of noise can create noticeable image artifacts, these characteristics create an enormous challenge for analog simulation tools, pushing both the accuracy and capacity simultaneously.

The presentation will highlight image sensor design and verification and include a description of Forza’s verification methodology, which uses a hierarchy of models for the image sensor blocks. At higher levels of the hierarchy, the complexity of the model is reduced, but the accuracy of the global interactions between blocks is maintained as much as possible.

CMOS Image Sensor Block Diagram

Forza’s verification flow relies on the Berkeley Design Automation (BDA) Analog FastSPICE (AFS) Platform. AFS is qualified on the latest TSMC Custom Design Reference Flow and, according to Forza, has significantly improved their verification flow.

Results will highlight how the AFS Full-Spectrum Device Noise, included in the latest TSMC Custom Design Reference Flow, validates that the sensitive ADCs and readout chain will withstand the impact of device noise and parasitics. For top-level sign-off, AFS AMS enables Forza to speed up verification by using Verilog to model non accuracy-critical circuits while maintaining nanometer SPICE accuracy on blocks that were independently verified in other tools. AFS Mega has the required capacity, speed, and accuracy required for us to perform verification of over 700 signal chains at the transistor level, including extracted parasitics.

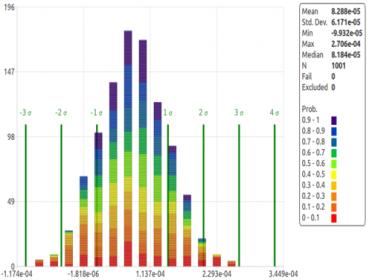

ACE Visual Distribution Analyzer – 1000 Iterations

In terms of characterization, Forza relied on BDA’s Analog Characterization Environment (ACE) to improve their characterization coverage and efficiency. Results include Monte Carlo-based analysis to predict image sensor nonuniformity due to device mismatch. Additionally, the AFS Circuit-Specific Corners, included in the latest TSMC Custom Design Reference Flow, efficiently eliminates the limitations of traditional digital process corners and generates circuit-specific corners for each measurement suitable for analog designs.

Evaluation

Datasheet

TSMC OIP

Also read: BDA Introduces High-Productivity Analog Characterization Environment (ACE)

lang: en_US

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.