We have seen last week in a first post how crucial was the IP qualification process (TSMC 9000) to increase the probability of successfully Tape Out a chip. Being able to discriminate between dangerous and safe IP is the first step of TSMC 9000 Quality process, IP tagging is the complementary step, almost as essential as the first … Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More Verification Analytics: The New Paradigm with Cogita-PRO at DVCON 2026Cogita-PRO, developed by Vtool, introduces a transformative approach…Read More

Verification Analytics: The New Paradigm with Cogita-PRO at DVCON 2026Cogita-PRO, developed by Vtool, introduces a transformative approach…Read More Breker Hosts an Energetic Panel on Spec-Driven VerificationI was fortunate to be asked to moderate…Read More

Breker Hosts an Energetic Panel on Spec-Driven VerificationI was fortunate to be asked to moderate…Read MoreOne-Stop Shop for Complete MIPI IP Solution

As we know mobile industry is one of the fastest growing in the electronics arena, and it has led to the emergence of several standards of interfaces between processors, devices, storage, camera, keyboard and so on. The interfaces can involve hardware as well as software and can be complex. The standards are still evolving, often… Read More

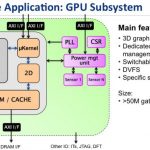

Carbon CEO on Advanceed ARM based SoC Design!

Carbon Design drives a lot of traffic to SemiWiki. Actually, it’s ARM driving traffic to the Carbon landing page since Carbon and ARM work closely together. When we blog about designing with ARM IP droves of people click over. Seriously, DROVES of people. Rick Lucier has deep EDA experience and has led Carbon as CEO for the … Read More

Methodics CEO on Managing Design Quality!

Methodics is new to SemiWiki and I have to tell you I’m really enjoying working with them. Their office is in a great location and the inovation spirit runs strong. Simon Butler is an interesting guy. He first started in EDA with HLD (acquired by Cadence) and was a founder at Sabio Labs (acquired by Magma). In between those startups… Read More

Power, Noise and Reliability Consideration for Advanced Automotive and Networking ICs

I love it when my Acura goes months and months without any major repair issue or computer-related glitches. Cars or networks only become reliable when they are designed and built for reliability. Freescale designs SoCs for advanced automotive and networking applications, and their engineers know much about the topics of power,… Read More

Qualcomm JEDEC Mobile Keynote: Memory Bandwidth and Thermal Limits

I went to some of the JEDEC mobile conference a couple of weeks ago. The opening keynote was by Richard Wietfeld of Qualcomm called The Need for Speed.

He emphasized that smartphones are really setting the pace these days in all things mobile and internet. Over 1/3 of access is on smartphones now. Over 4/5 of searches on smartphones… Read More

Chip and I/O Modeling for System-level Power Noise Analysis and Optimization

Cornelia Golovanovworks at LSI Corp in Pennsylvania and is an EMI expert that provides EDA tool and methodology advise to design groups. She earned a PhD in microelectronics and radioelectricity from the Institut national polytechnique de Grenoble, and joined Lucent out of school 12 years ago. We had a chance to talk by phone about… Read More

Jasper Low Power Verification App

Today, Jasper announced their new Jasper-Gold Low Power Verification App. This is focused on verifying low power designs with multiple power domains, voltage islands, power shutoff, clock shutoff, and all the other techniques used for reducing power. Of course power is the main driver of SoC design these days, whether it is for… Read More

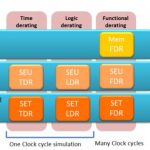

SOCFIT, Circuit Level Soft Error Analysis

I blogged recently about reliability testing with high energy neutron beams. This is good for getting basic reliability data but it is not really a useful tool for worrying about reliability while the chip is still being designed and something can be done about it.

That is where IROC Technologies SOCFIT tool comes in. It takes all… Read More

UVM/SystemVerilog: Verification and Debugging

At DAC in just three weeks you can learn about which EDA vendors are supporting the latest UVM 1.1d (Universal Verification Methodology) standard as defined by Accellera. One of those EDA vendors is Aldec, and they have a 45 minute technical session that you can register for online. Space will fill up quickly, so get signed up sooner… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?