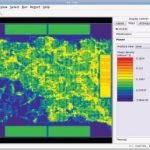

Thermal analysis has traditionally been given short shrift when compared to other more prominent issues facing chip designers. Invarian, to my eye at least, feels that the winds of change are in the air. Not that power or EM/IR issues will fade, that indeed is not the case and in fact quite the contrary, they are contributors to the… Read More

Verification Analytics: The New Paradigm with Cogita-PRO at DVCON 2026Cogita-PRO, developed by Vtool, introduces a transformative approach…Read More

Verification Analytics: The New Paradigm with Cogita-PRO at DVCON 2026Cogita-PRO, developed by Vtool, introduces a transformative approach…Read More Breker Hosts an Energetic Panel on Spec-Driven VerificationI was fortunate to be asked to moderate…Read More

Breker Hosts an Energetic Panel on Spec-Driven VerificationI was fortunate to be asked to moderate…Read MoreARM @ #50DAC

The 2013 Design Automation Conference celebrates its 50th anniversary Sunday, June 2 through Thursday, June 6 at the Austin Convention Center. DAC is the world’s leading technical conference and trade show on electronic design and design automation. DAC is where the IC Design and EDA ecosystem learns, networks, and does… Read More

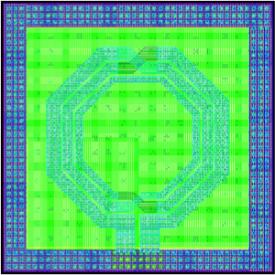

RFIC Design Challenges at #50DAC

RFIC developers used to favor mature silicon processes, typically staying back a couple of nodes behind the leading edge. This bought foundries time for ‘RF-enabling’ their PDKs, and also maximized return on investment for developing RF models and infrastructure IP. Not the case any more, it seems. To address the insatiable … Read More

SemiWiki Top 10 Must See @ #50DAC List!

This list was compiled by the SemiWiki bloggers highlighting emerging technologies that we have written about and that will be demonstrated at the Design Automation Conference next week. We highly recommend you investigate them further during your time in Austin and please let us know what you think.

Today SemiWiki has more than… Read More

Robust Reliability Verification: Beyond Traditional Tools and Techniques

Robust Reliability Verification: Beyond Traditional Tools

by Matthew Hogan, Mentor Graphics

At all process nodes, countless hours are diligently expended to ensure that our integrated circuit (IC) designs will function in the way we intended, can be manufactured with satisfactory yields, and are delivered in a timely fashion… Read More

Cooley’s Cheesy Must See List for DAC is Out

One of the other increasingly successful channels (besides Semiwiki of course) for EDA, IP and semiconductor companies to reach potential customers is John Cooley’s DeepChip. Every year he puts a lot of effort into trying to find out who is exhibiting what at DAC and which stuff seems like it is new and maybe important, and… Read More

ARM Partners with Carbon on Cortex-A57

Just in time for DAC, Carbon have announced that they have expanded their partnership with ARM to create and deliver models for the ARM Cortex-A57 processor and related IP. One piece of related IP is the Cortex-A53 which can be configured in big.LITTLE multi-core setups to achieve the sweet spot of higher performance and lower power.… Read More

10 years, 100,000 miles, or <1 DPM

Auto makers have historically been accused of things like planned obsolescence – redesigning parts to make repairs painfully or even prohibitively expensive – and the “warranty time-bomb”, where major systems seem to fail about a week after the warranty expires. Optimists would chalk both those up to relentless innovation,… Read More

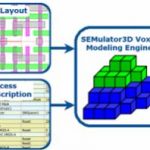

SEMulator3D – A Virtual Fab Platform

Yes, it’s a pleasant surprise; it is Virtual Fabrication Platform, one of the new innovations in 2013. I was looking around for what kind of breakthrough technologies will be announced in DAC this year. And here I came across this new kind of innovative tool which can produce final virtual fabricated 3D structures after following… Read More

You can tune a piano, but you can’t tune a cache without help

Once upon a time, designing a product with a first generation SoC on board, we were trying to use two different I/O peripherals simultaneously. Seemed simple enough, but things just flat out didn’t work. After days spent on RTFM (re-reading the fine manual), we found ourselves at the absolute last resort: ask our FAE.

After about… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?