Tools, tools, tools. Designs are rapidly changing, JESD204b, Hybrid Memory cube and all other Gigabit serialization schemes are here to stay. RIP DDR. This means board level simulations with respect to firmware (FPGA) are going to be more challenging than ever. Why? you ask, especially if the board layout is simpler? True, but… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read MoreFive Things You Don’t Know About MunEDA

So first the one thing that you do know. MunEDA are based in Munich which makes them German. I have to confess that until I got involved helping them a bit with some marketing stuff that that was about all I knew about them too.

So now five things that you might not know:

1. MunEDA have a much wider customer list that you know and would even… Read More

Xilinx KCU105 Evaluation board is key for your demo

I love God, my wife, kids, and FPGA boards. I know I am not alone, there are other nerds out there, don’t be shy. Friday my “Kintex® UltraScale™ FPGA KCU105 Evaluation Kit” came in. Think about this, this is real 20nm Xilinx FPGA hardware that really works. Below is a nice picture of all the swizzles the board has.

I believe this is the … Read More

National Semiconductor Education in the Cloud

“I wandered lonely as a cloud,” wrote Wordsworth. Well, clouds are pretty lonely in EDA these days. Despite some of the advantages on paper that mean that companies from salesforce.com to Netflix make heavy use of cloud-computing, semiconductor design has barely touched the cloud. One exception was Nimbic (acquired… Read More

Product Marketing & the Butterfly Effect

I often feel that product marketing can simultaneously be an underrated and overrated function. More often than not, it suggests product goals, pricing, and positioning. Then the marketing department must defend those positions to both engineering and sales. However, both the engineering and sales departments can claim expertise… Read More

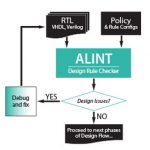

FinFET Based Designs Made Easy & Reliable

Although semiconductor manufacturing has taken off with FinFET based process technology which provides lucrative payoffs on performance improvement, power reduction and area saving in devices for high density and high performance SoC demand of modern era, apprehensions remain about its reliability due to reduced noise … Read More

SemiWiki is an Open Forum for Semiconductor Professionals!

Why should you be a part of SemiWiki? Two reasons: One, SemiWiki is an excellent semiconductor networking tool. Quite often “who you know” comes into play in your professional life so network-network-network. Two, SemiWiki is all about personal branding. Establish yourself as a person of interest in your chosen field and opportunities… Read More

EDA for Power Management ICs at DAC

I first met Dundar Dumlugolat Barcelona Design back in 2004, so it was a pleasure to meet with him again at DAClast week and learn more about what his company Magwel has to offer IC designers of power management chips.… Read More

Sensor Hub and Wearable Gestures

One of the challenges with the internet of things (IoT) is that many devices are both always on and battery powered (and not with a large battery). The responsibilities need to be split so that the device senses when it needs to wake up without requiring the application processor to be waking up all the time to make the decision since… Read More

SEMICON West 2014 Event Calendar

SEMICON West is the flagship annual event for the global microelectronics industry. It is the premier event for the display of new products and technologies for microelectronics design and manufacturing, featuring technologies from across the microelectronics supply chain, from electronic design automation, to device … Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era