Apple’s dismal earnings announcement shows why it badly needs to rethink its innovation model and leadership. Its last breakthrough innovation was the iPhone — which was released in 2007. Since then, Apple has simply been tweaking its componentry, adding faster processors and more advanced sensors, and playing with … Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More3D NAND – Moore’s Law in the third dimension

For more than a decade 2D NAND has been the leading driver of lithography shrinks, for example, Samsung went from 120nm in 2003 to 16nm in 2014 with shrinks on an almost yearly basis, but the shrinks came at a price. At 16nm Self Aligned Quadruple Pattering (SAQP) was required for the most critical layers and patterning related costs… Read More

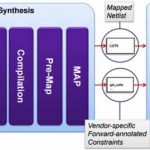

One FPGA synthesis flow for different IP types

Both Altera and Xilinx are innovative companies with robust ecosystems, right? It would be a terrible shame if you located the perfect FPGA IP block for a design, but couldn’t use it because it was in the “wrong” format for your preferred FPGA. What if there were a way around that?

There is a compelling argument to use each FPGA vendor’s… Read More

Neural nets for Qualcomm Snapdragon

Neural nets are hot these days. In this forum certainly you can’t swing a cat without hitting multiple articles on the topic – I’ve written some myself. For me there are two reasons for this interest. First, neural nets are amazingly successful at what they do, for example in image recognition where they can beat… Read More

Seven Reasons to Attend DAC in Austin

I’m attending the 53rd Design Automation Conference (DAC) in Austin, Texas starting June 5th, and there are at least seven reasons that you should consider attending as well. For decades now DAC has been the premier place for all the players in our semiconductor ecosystem to get together: Academics, Commercial vendors … Read More

Is the Future Finally Here? What a GaAs!

Back in 1983 I was working for Texas Instruments during the beginning of the push to let common electrical engineers develop their own CMOS application specific ICs (ASICs). This would eventually the be the fuel that fed the semiconductor engine to reach over $335 billion in 2015. At that time, I was a young guy and I had a rascally … Read More

Qualcomm’s New Smartphone Chips Go Straight At MediaTek

Last Thursday at Qualcomm’s Financial Analyst Day the company made a slew of chip announcements ranging from the industry’s 1 Gbps wireless LTE modem to a custom designed smartwatch SoC and platform called “Snapdragon Wear 2100 SoC”. In between those, Qualcomm also announced a few very overlooked … Read More

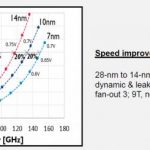

Are Standard Cell Libs, Memories and Mixed-signal IP Availabe at 7nm FF?

More than 500 designers (562) have responded to a survey made in 2015 by Synopsys. Answering to the question “What is the fastest clock speed of your design?” 56% have mentioned a clock higher than 500 MHz (and still 40% higher than 1 GHz). If you compare with the results obtained 10 years ago, the largest proportion of answers was for… Read More

Body-biasing for ARM big or LITTLE in GF 22FDX

GLOBALFOUNDRIES has been evangelizing their 22FDX FD-SOI process for a few months; readers may have seen Tom Simon’s write-up of their preview at ARM TechCon. Dr. Joerg Winkler recently gave an updated webinar presentation of their approach in an implementation of ARM Cortex-A17 core.

By now, you’ve probably heard that 22FDX… Read More

Eight Improvements for PCB Software

I first met John Durbetaki at Intel in Aloha, Oregon and we both had a keen interest in the nascent personal computer industry. My first PC was made by Radio Shack and dubbed the TRS-80 which maxed out at 48KB of RAM. I kept watch on Durbetaki as he left Intel and formed his own company OrCAD in 1985 to serve the needs of PC-based CAD software.… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center