In a keynote at the 62nd Design Automation Conference (DAC) on July 8, 2025, William Chappell, Vice President of Mission Systems at Microsoft, reflected on the intertwined evolution of AI and semiconductor design. Drawing from his DARPA experience, Chappell traced AI’s progression from 2016 onward, highlighting its… Read More

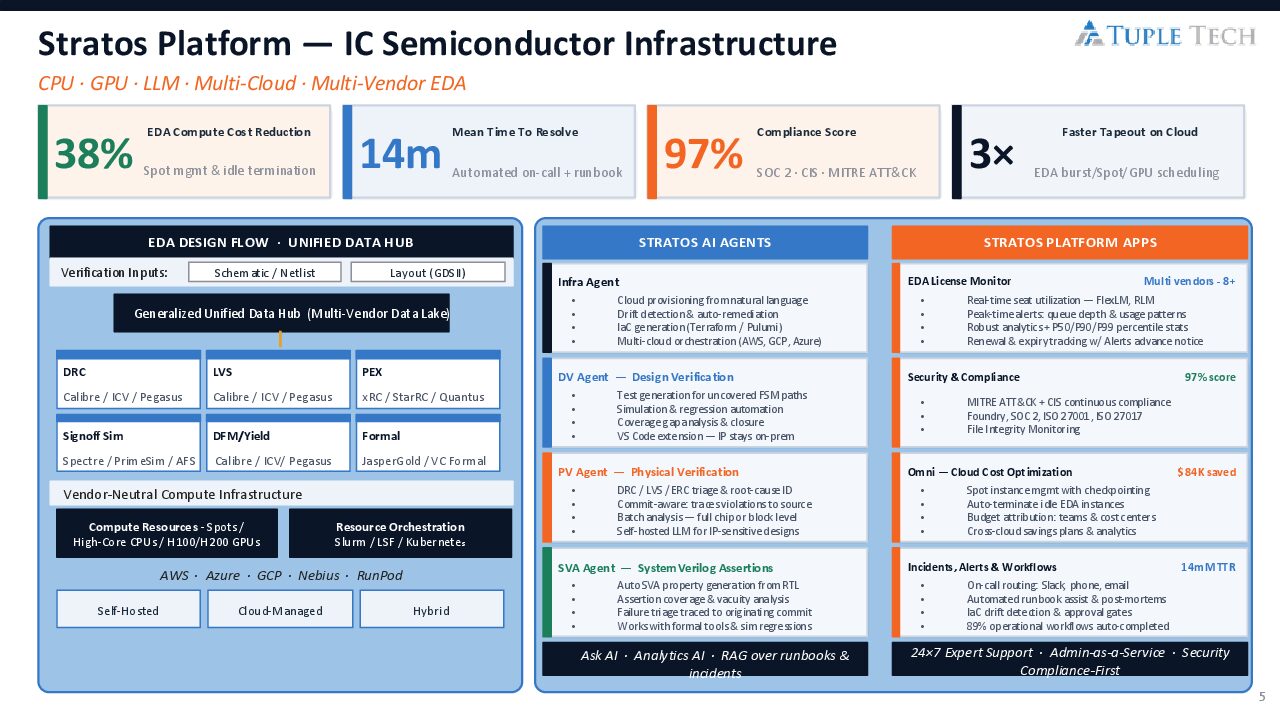

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read More

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read MoreAI-Driven ECAD Library Creation: Streamlining Semiconductor Design

On July 9, 2025, Julie Liu, PalPilot International presented for DACtv, unveiling Footprintku AI, a groundbreaking platform for automating configurable ECAD (Electronic Computer-Aided Design) library creation. This innovative solution addresses the inefficiencies of manual library generation, leveraging AI and … Read More

Modern Data Management: Overcoming Bottlenecks in Semiconductor Engineering

In a DACtv session on July 9, 2025, Pedro Pires from Keysight’s Design Engineering Software addressed the critical role of data management in modern semiconductor engineering projects. The presentation highlighted why data has become a bottleneck, how Keysight’s SOS (Save Our Source) platform mitigates these challenges,… Read More

Formal Verification: Why It Matters for Post-Quantum Cryptography

Formal verification is becoming essential in the design and implementation of cryptographic systems, particularly as the industry prepares for post-quantum cryptography (PQC). While traditional testing techniques validate correctness over a finite set of scenarios, formal verification uses mathematical proofs to guarantee… Read More

CEO Interview with Bob Fung of Owens Design

Bob Fung is the CEO of Owens Design, a Silicon Valley company specializing in the design and build of complex equipment that powers high-tech manufacturing. Over his 22-year tenure, Bob has led the development of more than 200 custom systems for world-class companies across the semiconductor, biomedical, energy, and emerging… Read More

Podcast EP301: Celebrating 20 Years on Innovation with yieldHUB’s John O’Donnell

Dan is joined by John O’Donnell, Founder and CEO of yieldHUB, a pioneering leader in advanced data analytics for the semiconductor industry. Since establishing the company in 2005 he has transformed it from a two-person startup into a trusted multinational partner that empowers some of the world’s leading semiconductor companies… Read More

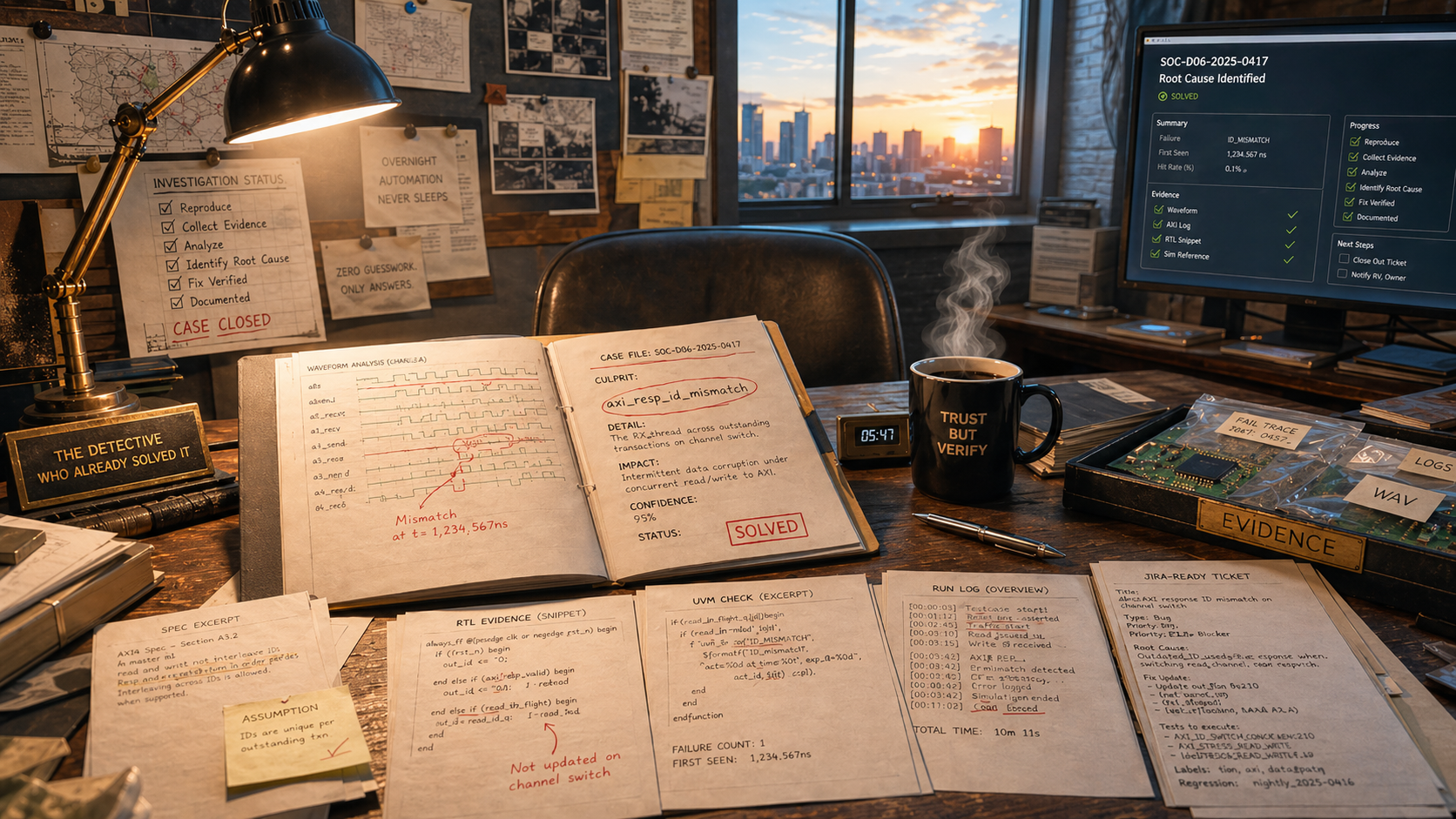

AI-Powered Waveform Debugging: Revolutionizing Semiconductor Verification

On July 9, 2025, a DACtv session with Zackary Glazewski of ChipAgents AI introduced Waveform Agents, an AI-driven solution by Chip Agents designed to tackle the complex challenge of waveform debugging in semiconductor design. The speaker highlighted the difficulties of traditional waveform debugging and demonstrated how… Read More

AI-Driven Verification: Transforming Semiconductor Design

In a DACtv session on July 9, 2025, Abhi Kolpekwar, Vice-President & General Manager at Siemens EDA, illuminated the transformative role of artificial intelligence (AI) in addressing the escalating challenges of semiconductor design verification. The presentation underscored the limitations of traditional methods… Read More

Building Trust in AI-Generated Code for Semiconductor Design

On July 9, 2025, a compelling session at DACtv by Vishal Moondrha of Perfroce addressed a critical challenge in the semiconductor industry: building trust in AI-generated code. The speaker highlighted the unique hurdles of integrating generative AI into semiconductor design, emphasizing issues like data provenance, quality,… Read More

CEO Interview with Andrew Skafel of Edgewater Wireless

As the demand for high-capacity, low-latency wireless networks explodes across residential, enterprise, and industrial environments, a Canadian innovator is quietly reshaping the way Wi-Fi works—from the silicon up. Edgewater Wireless (TSXV:YFI/OTC:KPIFF), headquartered in Ottawa, is pioneering a transformative… Read More

Siemens U2U 3D IC Design and Verification Panel