You might have thought that ultra-low power communication for the IoT was limited to standards like BT5 and 802.15.4 (eg in ZigBee and Thread) which depend on gateways to cellular networks and limit reach, especially deep inside buildings. But now there’s a new standard for ultra-low power and ultra-low cost based on LTE, known… Read More

Sensors Converge: Where Intelligence Meets the EdgeThe Sensors Converge Conference is one of the…Read More

Sensors Converge: Where Intelligence Meets the EdgeThe Sensors Converge Conference is one of the…Read More Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read MoreMentor’s Battle of the Photonic Bulge

A few weeks back I wrote an article mentioning that Mentor Graphics has been quietly working on solutions for photonic integrated circuits (PICs) for some time now, while one of their competitors has recently established a photonics beachhead. One of the most common challenges for PIC designs is their curvilinear nature, thus… Read More

Qualcomm Brings Us One Step Closer To Gigabit LTE Speed Products

Qualcomm announced at their 4G/5G Summit in Hong Kong specific products their 1 Gigabit Snapdragon X16 LTE modem will ship inside of. In February, the company announced, as we wrote in Forbes last Febraury here, that they had achieved speeds of up to 1 Gbps using this newly-announced Snapdragon X16 modem. Many questioned when we… Read More

Dark data to fuel warp speed growth for #IoT

In my world of semiconductors, dark silicon refers to transistors that are present in the chip but that can not be turned on due to thermal constraints. A valid resource that is available but not used. In the case of #IoT we have a lot of data already out there that I would label as dark data, it exists but no one outside the network owner… Read More

Hack This? Making Software a Moving Target

It sometimes seems that the black hats are always one step ahead of the white hats in the never-ending security game. One of the especially invidious ways hackers have found to evade detection is through mutation – changing the code in a virus on each copy, defeating classical signature detection methods and potentially requiring… Read More

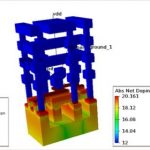

It’s Better than SUPREM for 3D TCAD

Process and device engineers have a tough task to model and simulate an IC process prior to fabricating silicon, however this approach is much better than the alternative choice in the 1970’s of just running multiple lots of wafers and then making measurements to see if your node was meeting specifications. Out of Stanford… Read More

The Future of FPGA Prototyping!

This interview originally appeared as the foreword to our book “Prototypical: The Emergence of FPGA-based Prototyping for SoC Design” but I thought it would be worth publishing for those of you who have not downloaded it yet. I also wanted to mention that our friends at S2C are currently offering a 50% discount on the… Read More

It’s Apple TomTom Time Again

It’s December and time for the annual Apple-should-buy-TomTom rant. Of course, we know Apple prefers younger, smaller companies with brighter and clearer long-term prospects, but we also know Apple navigation sucks and if there is one thing TomTom does well it’s navigation… and traffic.

To stir the pot, … Read More

How The Snapdragon X50, World’s First 5G Modem, Puts Qualcomm Ahead Of The Curve

Regardless of what part of technology you come from, the entire tech industry has been talking about 5G. 5G will reshape the way we will use mobile devices, deliver self-driving cars and smart cities, and even the way get content delivered to our homes. Some companies talk about it to be part of the conversation, while others lead … Read More

CEO Interview: Randy Caplan of Silicon Creations

For the next installment in our series of semiconductor CEO interviews we meet with Randy Caplan from Silicon Creations. Randy has helped build the company from a small startup to one of the world’s leading providers of interface and clocking IP. Almost every new chip developed these days has a requirement for PLLs and SerDes. Since… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center