Adi Gelvan is a veteran tech executive and serial entrepreneur, currently serving as the CEO of SPEEDATA, a semiconductor startup redefining analytics infrastructure with its purpose-built Analytics Processing Unit (APU). Known for his sharp operational instincts and deep technical insight, Adi joined Speedata in 2025 … Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More

Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More #DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read More

#DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read MorePodcast EP346: How EMD Electronics Bridges the “Lab to Fab” Gap With Ganesh Panaman

Daniel is joined by Ganesh Panaman, the President of Intermolecular Services at EMD Electronics. In his current role, Ganesh is dedicated to accelerating product time-to-market, securing first-mover advantages on disruptive technologies, and actively engaging with the dynamic startup ecosystem in the Silicon Valley. … Read More

TSMC’s Record Tool Orders Hint at Another CapEx Shockwave

TSMC’s latest Board of Directors capital appropriation announcement may appear mixed on the surface, but a closer look reveals one important conclusion: The company is quietly setting the stage for another potential upward revision to its already aggressive 2026 capital expenditure outlook. The headline figure of $31.3B … Read More

CEO Interview with Nagesh Gupta of llmda.ai

Nagesh has built a career spanning multiple aspects of system design and development at companies including Hewlett-Packard, Cadence, Xilinx, and Lattice Semiconductor.

He is also a serial entrepreneur. Nagesh founded Taray, Inc., which developed memory interface generators for Xilinx designs and was later acquired by … Read More

The “New Shift-Left”: Why FPGA Prototyping is the Ultimate RISC-V IP Sandbox

In the EDA world, “Shift-Left” has traditionally been a mantra for early software development—booting the OS before the silicon even leaves the fab. But as the RISC-V revolution accelerates, the goalposts have moved. We are seeing the emergence of a “New Shift-Left”, one that focuses on critical architectural… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!

May’s WSTS Report saw March’s total monthly semiconductor sales up 88.1 percent vs. March 2025, albeit down 8.5 percent from February 2026. This month-on-month decline needs to put in the context of February’s record-breaking 25.7 percent monthly growth.

This growth, however, was solely attributable to ICs, up 99.5 percent… Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI Era

With the launch of its new P570 Gen 3 processor family, SiFive is making a broader statement about the future of edge computing and the growing role of RISC-V in mainstream application processors. Rather than simply unveiling another CPU core, the company is positioning the P570 as a balanced-performance processor built specifically… Read More

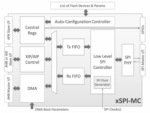

Configurable xSPI memory controller IP core is FuSa-ready

SPI, invented some four decades ago, is so successful as a low-pin-count interface for microcontrollers and processor cores that it spurred memory makers to incorporate both the physical signaling interface and advanced memory command protocols into serial flash and serial pseudo-SRAM (PSRAM) devices. Those protocols, … Read More

CEO Interview with Dr. Jekaterina Viktorova of Syenta

Dr. Jekaterina (Jeka) Viktorova is the CEO and Co-Founder of Syenta, an Australian deep-tech company developing breakthrough additive manufacturing technology for the semiconductor industry. With a background in chemistry, electrochemistry, and advanced manufacturing, she is the inventor of the core Syenta technology… Read More

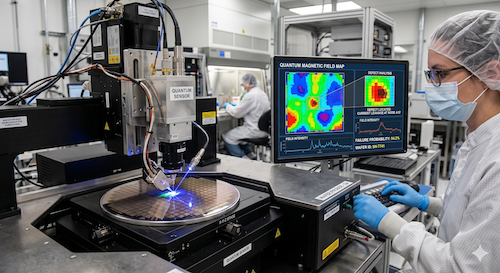

Sensing. A Quantum Tech Ready for Market?

While the quantum world revolves around quantum computing, (QC) there are a couple of other quantum technologies of note. I covered one of these, quantum communication, in a recent blog. Here I’ll introduce the other, quantum sensing. The goal is to use the high sensitivity of an individual quantum state to external factors such… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior