You might not immediately see a connection between semiconductor substrate choices and inference at the edge. These technology layers seem worlds apart and yet SOITEC have a point. Edge AI has rapidly evolved from simple CNNs to now complex reinforcement learning systems and transformer based LLMs. Even when shrunk to edge footprints,… Read More

Sensors Converge: Where Intelligence Meets the EdgeThe Sensors Converge Conference is one of the…Read More

Sensors Converge: Where Intelligence Meets the EdgeThe Sensors Converge Conference is one of the…Read More Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More2024 Outlook with Cristian Amitroaie, Founder and CEO of AMIQ EDA

SemiWki has been working with AMIQ EDA for more than four years now and it has been quite the education. AMIQ EDA is a company that specializes in providing development and verification solutions for digital design and verification teams in the semiconductor industry. They offer a range of products and services aimed at improving… Read More

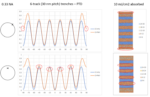

Application-Specific Lithography: Avoiding Stochastic Defects and Image Imbalance in 6-Track Cells

The discussion of any particular lithographic application often refers to imaging a single pitch, e.g., 30 nm pitch for a 5nm-family track metal scenario. However, it is always necessary to confirm the selected patterning techniques on the actual use case. The 7nm, 5nm, or 3nm 6-track cell has four minimum pitch tracks, flanked… Read More

2024 Outlook with Thomas Gerner Nørgaard, Founder Comcores

SemiWiki has been working with Comcores for two years. They are very active in the semiconductor ecosystem and highly regarded.

Comcores specializes in providing digital intellectual property (IP) solutions and design services for communication and networking technologies. They focus on developing and delivering IP cores,… Read More

proteanTecs Addresses Growing Power Consumption Challenge with New Power Reduction Solution

proteanTecs is a unique company, delivering electronics visibility from within. Its core mission is to enable the electronics industry to continue to scale. The company achieves this goal by first embedding on-chip monitors, called Agents, during the design process to generate deep data on the chip’s profiling, health, and… Read More

2024 Outlook with Toshio Nakama of S2C

Tell us a little bit about yourself and your company.

I am Toshio Nakama, the founder and CEO of S2C and a strong advocate of FPGA accelerated ASIC/SoC design methodology. I first started my career at Altera as an FAE and served in technical and sales management roles at Aptix Corporation. I co-founded S2C in Silicon Valley in 2003 … Read More

Expedera Proposes Stable Diffusion as Benchmark for Edge Hardware for AI

A recent TechSpot article suggests that Apple is moving cautiously towards release of some kind of generative AI, possibly with iOS 18 and A17 Pro. This is interesting not just for Apple users like me but also for broader validation of a real mobile opportunity for generative AI. Which honestly had not seemed like a given, for multiple… Read More

What ChatGPT has to say about the Chiplet Summit

Quite a few of the articles I now see about the semiconductor industry use AI. It is not hard to tell, especially for someone like myself, a 40 year experienced semiconductor professional who also writes. In the last 13 years (yes SemiWiki is now a teenager) we have published 9,058 blogs. SemiWiki was the first of now many semiconductor… Read More

Podcast EP206: An assessment of the Chiplet Ecosystem Movement with Alphawave’s Tony Chan Carusone

Dan is joined by Tony Chan Carusone, Chief Technology Officer of Alphawave Semi. Tony has been a professor of Electrical and Computer Engineering at the University of Toronto since 2001 and has served as a Distinguished Lecturer for the IEEE Solid-State Circuits Society and on the Technical Program Committees of the world’s leading… Read More

CEO Interview: Jay Dawani of Lemurian Labs

Jay Dawani is the co-founder and CEO at Lemurian Labs, a startup developing an accelerated computing platform tailored specifically for AI applications. The platform breaks through the hardware barriers to make AI development faster, cheaper, more sustainable, and accessible to more than just a few companies.

Prior to founding… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center