Two approaches compared

With half-pitch approaching 10 nm, EUV patterning is heavily impacted by stochastic effects, which are aggravated from reduced image contrast from electron blur [1]. A two-mask (“LELE”: Litho-Etch-Litho-Etch) approach was proposed to pattern core features for self-aligned double patterning (SADP) to get to design rules expected for 2nm node [2], in order to handle the wide and narrow linewidths of the 6-track cell. However, this LELE patterning still suffers from sensitivity to overlay due to two masks being used. In this article, we look at two approaches which use one mask, which can be applied to any number of tracks.

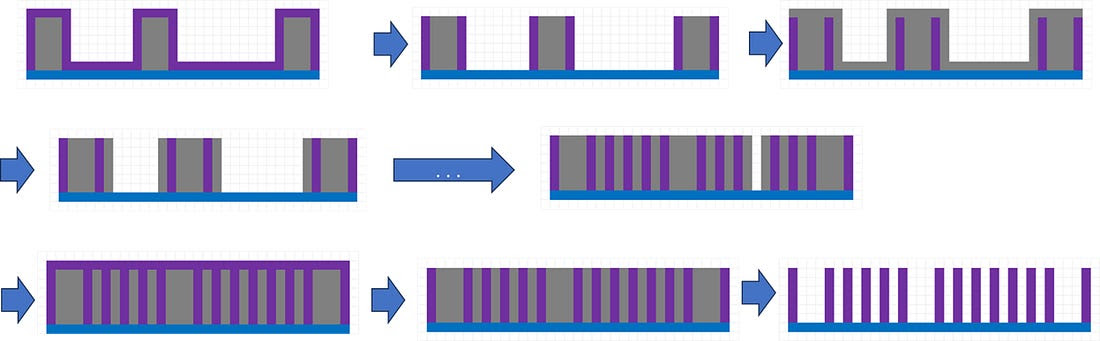

Multiple Deposition-Etch

The multiple deposition-etch approach is described in the expired patent US10325777 [3]. As shown in Figure 1, it is basically a sequence of iterations of deposition followed by etch. Each iteration produces a sidewall spacer adjacent to a sidewall spacer from the previous iteration. The number of iterations depends on the largest cell height. In Figure 1 it is the 8-track cell toward the right. Six deposition-etch iterations are required.

A couple of important comments need to be made. First, it should go without saying that etching the purple material must be highly selective against the gray and cyan materials, and the etching of the gray material must be highly selective against the cyan materials. Likewise, the final etch of the cyan substrate layer should be sufficiently selective against the purple material as the etch mask.

The second point is that the etch profiles of the etched spacers are not expected to be rectangular. The top of the spacer is expected to be etched more at the outward exposed side, leading to a horn-like shape from asymmetric sidewall erosion. For a few iterations, this may not be too much of a concern, but with several or more iterations, the danger is that the last few spacers are moved from their target positions from the accumulated sidewall erosions. Thus, an alternative approach we consider next may be helpful.

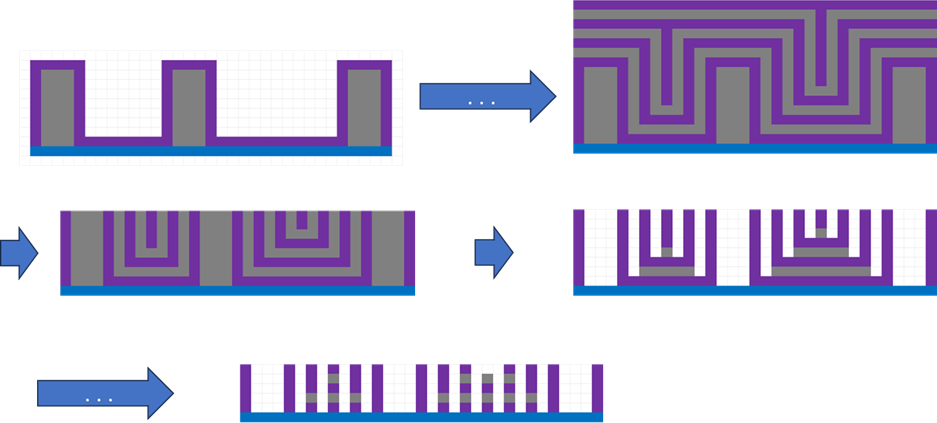

Multilayer-Spacer

The multiple-layer spacer approach is described in the expired patents US6300221 [4] and US7919413 [5]. Rather than iteratively alternating deposition and etch, all the layer depositions are done at once conformally, such as with atomic layer deposition (ALD); then all the etching is done (Figure 2). The etching after spacer multilayer deposition has also been demonstrated after gate patterning [6].

This approach avoids the horn-like appearance since there is no asymmetry from the outward facing spacer corner; each spacer top is equally surrounded on both sides. Consequently, the position of each spacer doesn’t change. On the other hand, this approach does require the starting features to be sufficiently tall so that enough alternating spacers fit in between with the conformal deposition. In the case of Figure 2, the initial features need to exceed 7 spacer layers in height. Similar to the case of the multiple deposition-etch approach above, this is linked to the largest cell height determining the required number of alternating spacer material layers.

The Ultimate Pitch Reduction Booster

If we take the spacer thickness to be 10 nm, then the minimum lithographic pitch for the structure of Figures 1 and 2 is 120 nm, for the 6-track cell on the left. The pitch for the 8-track cell on the right is 160 nm. Thus, pitch reductions of 6x and 8x respectively are shown by these approaches. The required lithographic pitch is easily achievable with an ArF immersion scanner with a numerical aperture of 1.2 or higher. Thus, both the multiple deposition-etch and multilayer spacer approaches above are extremely effective scaling boosters going beyond lithography in reducing pitch.

References

[1] F. Chen, A Realistic Electron Blur Function Shape for EUV Resist Modeling.

[2] F. Chen, Rethinking Multipatterning for 2nm Node.

[3] US10325777, filed by IBM.

[4] US6300221, assigned to Intel.

[5] US7919413, assigned to ITRI.

[6] C-J Weng, Microel. Rel. 50, 1951 (2010).

Also Read:

A Realistic Electron Blur Function Shape for EUV Resist Modeling

Rethinking Multipatterning for 2nm Node

Share this post via:

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center