One-time programmable (OTP) non-volatile memory has been around for a long time. Compared to other non-volatile memory technologies OTP has a smaller footprint and does not require additional manufacturing steps, making it a popular choice to store items such as boot code and encryption keys. While this sounds simple, the growth of ubiquitous AI deployment and the associated demand for more advanced technology make balancing the demands of OTP quite challenging.

These devices play a critical role to securely store data, sensitive program code, product information, and encryption keys for authentication. The devices must operate reliably to achieve a successful chip, and the spiraling cost of new technologies makes the stakes quite high. But advanced nodes present many challenges to ensuring OTP memories work reliably. Getting it right can become a substantial balancing act. The good news is there is a path to balancing the demands of OTP for advanced nodes with Synopsys IP.

What’s at Stake?

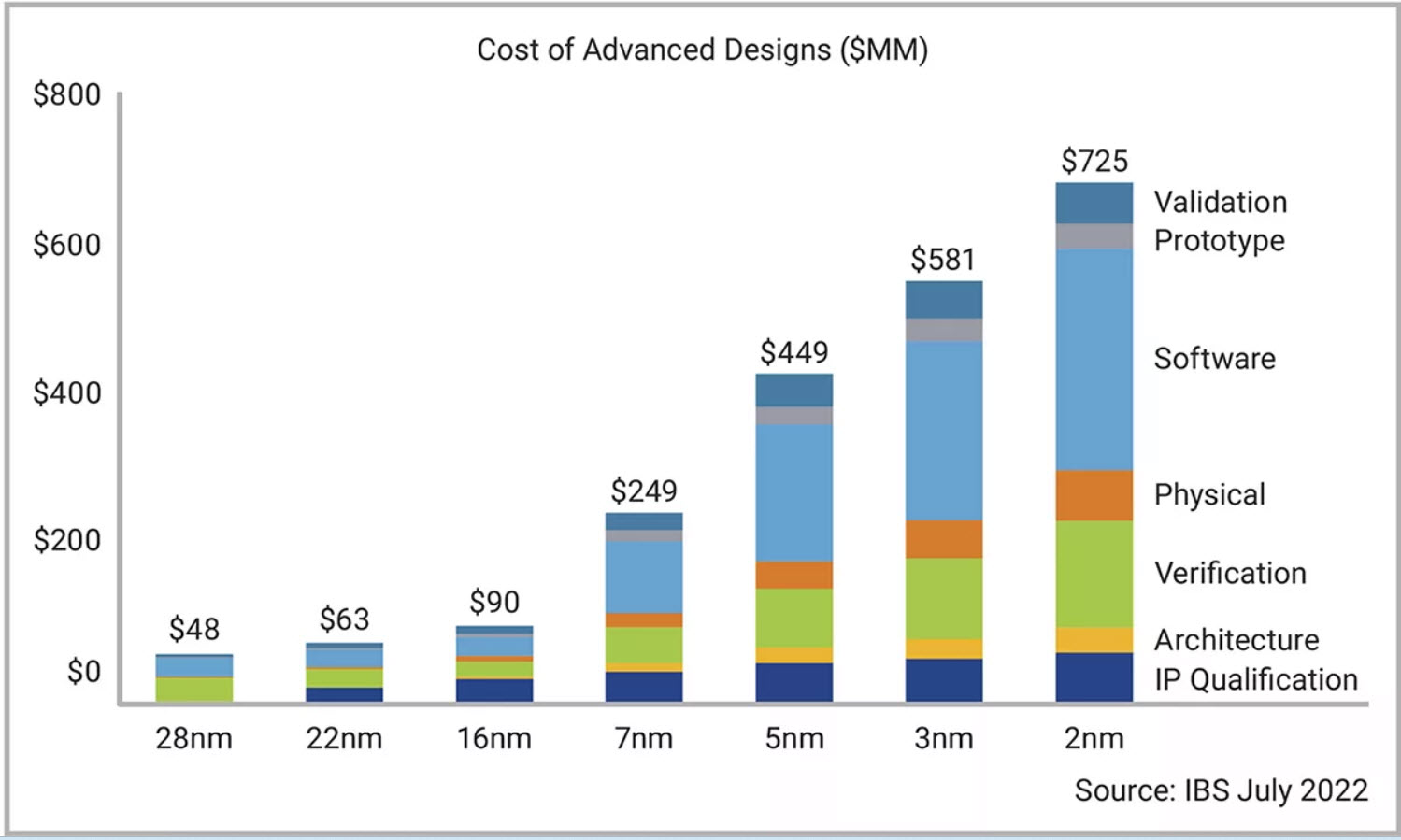

Spiraling design, mask, and wafer costs in advanced FinFET nodes make achieving first-pass success more important than ever. And reliable IP operation, and in particular the critical functions that OTP IP enable are directly on the path to success. The figure below illustrates how fast these costs are mounting for advanced technologies.

OTP IP delivers critical data that unlocks the functions of advanced, AI-based designs. This data is highly sensitive, so accurate delivery of the information is required. And compromise of information such as encryption keys cannot be tolerated. Against these stringent requirements there are many factors to consider. Let’s look at some of them.

Barriers to Success

Let’s start with the basics. For typical antifuse OTP memory, unprogrammed cells represent a logic value of 0 and programmed cells represent a logic value of 1. When these devices are first manufactured, all cells are unprogrammed and so they are at logic 0. Programming cells involves the application of high voltage to the cells -. The high voltage results in a breakdown of the oxide and formation of a channel or filament, creating a current path that can be measured.

So, reading an OTP requires measuring the gate leakage current to determine if the cell is programmed (logic 1) or unprogrammed (logic 0). This involves using regulated voltages above the core supply voltage to get enough current on the bit lines to reliably read the data.

So far, this sounds straightforward. But technology advances make the process challenging.

Advanced nodes have thinner oxides, so reading at regulated voltages above the core supply voltage makes the OTP more susceptible to leaky bits and misreading bits as logic 1 even when they are not programmed. Thinner oxide also creates higher device stress on unprogrammed cells within the word being read.

In addition, advanced nodes have higher device leakage. This means using higher voltages to drive sufficient current for programming the OTP. These higher voltages can result in damage, leading to programming failures. And due to the thinner oxide, advanced node OTP is more susceptible to high voltages and may become over-programmed. Over programming an OTP can result in poor programming quality and unnecessary over-exposure of the cells to high voltage. To make things worse, high voltage can cause program disturbs, where unintended neighboring cells are accidentally programmed, causing other errors.

There are also a host of PPA challenges to be dealt with. Higher leakage can make it difficult to keep the OTP area competitive and may limit the maximum bit count for reliable operation. Also, the total cost of manufacturing is affected by programming time. Programming the OTP requires a significant increase in voltage. As supply voltages are lower in advanced nodes, it may take longer to ramp up the voltages to drive the programming currents and successfully program the OTP, resulting in more time and cost.

Techniques to Balance Requirements for Success

Here is a subset of the requirements.

A reliable solution starts with bitcell design. The quality of the filament formed during programming depends on how well the oxide is broken, which in turn depends on the bitcell area. If it’s too small, breaking the oxide and forming the filament becomes difficult, leading to programming failures. If it’s too large, multiple breaks in the oxide may occur during programming.

All of this can create errors in reading critical data. So, the bitcell area must be carefully chosen to optimize the formation of the filament during programming to prevent error conditions, ensuring reliable programmability.

OTPs rely on high voltages for both reading and programming. These voltages are generated and regulated by an analog integrated power supply (IPS). The design of this device is critical for the correct functioning of the OTP as variations in the required voltages will result in data retention issues or errors.

Also, the data output from the OTP during reads must always be reliable. Ensuring the integrity of the data read is crucial. Signals that flag the OTP output as good-to-go are essential to weed out unintended data corruption from voltages that are not stable during reads.

In addition, the high device leakage for advanced nodes requires intervention to ensure not only reliability but also that performance and power targets are met for the OTP. The length of the bitlines and the width of the memory array must be carefully designed to avoid excessive IR drop when the memory is operating.

And finally, optimized analog design is key. For example, the sense-amplifiers must be particularly sensitive to the low voltages typical of advanced nodes to ensure programming speed, which impacts manufacturing cost and needs to be optimized through expert design of the high-voltage circuitry. Achieving this is challenging due to conflicting requirements. That is, the need to minimize the overall area of the OTP while still providing enough current from the charge pump in the IPS to successfully program the memory.

Synopsys Delivers the Solution

Synopsys OTP NVM IP for advanced nodes starts with the design of a robust, optimized anti-fuse bit cell. The design has been proven over high temperature operating life (HTOL) tests. This design balances all the requirements discussed above.

The solution includes a memory array composed of tiled bit cells, decoders, analog components such as sense amplifiers, and an IPS that generates the necessary voltages for reads and programming. The choice of read voltage ensures reliable bit cell reads and guarantees data retention for at least 10 years.

The IP is enhanced with additional bits to insure against random manufacturing defects and field failures. Each word is equipped to correct a leaky bit and/or a programming failure during initial testing. Additional repair resources are available for multiple failures within a word, and entire words can be replaced if necessary. The OTP memory array also includes additional bits for storing error correction codes (ECC).

The IP is available in a wide range of configurations, enabling selection of the optimum options for each application. A controller that manages the reads and writes, test-and-repair, and ECC encoding and decoding is part of the overall solution. The controller is delivered as soft IP in the form of RTL, with the OTP memory array and IPS integrated into a single hard macro.

Substantial security capabilities are also part of the package.

To Learn More

I have really just scratched the surface on the capabilities available from Synopsys for optimized implementation of OTP memory. Almost every design these days will require some form of OTP to correctly enable operation. It is worth your time to see how Synopsys can help you tame the balancing act required to get your design working reliably at advanced nodes.

An informative article is available here: Achieving Reliable and Secure SoC Designs with Advanced OTP IP. A comprehensive datasheet for the package is available here. And you can visit the webpage on Synopsys Non-Volatile Memory IP here. There are many additional resources there. And that will provide you with what’s needed to understand balancing the demands of OTP for advanced nodes with Synopsys IP.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.