Array

(

[content] =>

[params] => Array

(

[0] => /forum/threads/isscc-n2-and-18a-has-same-sram-density.22126/

)

[addOns] => Array

(

[DL6/MLTP] => 13

[Hampel/TimeZoneDebug] => 1000070

[SV/ChangePostDate] => 2010200

[SemiWiki/Newsletter] => 1000010

[SemiWiki/WPMenu] => 1000010

[SemiWiki/XPressExtend] => 1000010

[ThemeHouse/XLink] => 1000970

[ThemeHouse/XPress] => 1010570

[XF] => 2031070

[XFI] => 1060170

)

[wordpress] => /var/www/html

)

Guests have limited access.

Join our community today!

Join our community today!

You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please, join our community today!

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

ISSCC N2 and 18A has same SRAM Density.

- Thread starter siliconbruh999

- Start date

siliconbruh999

Well-known member

siliconbruh999

Well-known member

a 33% difference increase in frequency at iso voltage that is ridiculous difference5.6 vs 4.2 GHz @ 1.05 volts.. oof...

Xebec

Well-known member

How do we compare the SRAM speed vs previous nodes. TSMC N5 SRAM was shown as 4.1 GHz @ 0.85V in March 2020: (I can't find any public info for N4 or N3) :

semiwiki.com

semiwiki.com

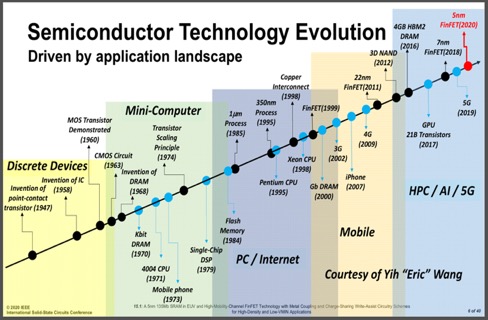

TSMC’s 5nm 0.021um2 SRAM Cell Using EUV and High Mobility Channel with Write Assist at ISSCC2020 - Semiwiki

Technological leadership has long been key to TSMC’s success and they are following up their leadership development of 5nm with the world’s smallest SRAM cell at 0.021um 2 with circuit design details of their write assist techniques necessary to achieve the full potential of this revolutionary...

siliconbruh999

Well-known member

Does the macro size affects frequency?

jorgequinonez

Member

That's basically like a half-node increase in clock speed for the same voltage! Will be interesting to see how much TSMC's A16 node closes the gap compared to Intel's 18A node.

MKWVentures

Moderator

perhaps we should not judge an entire node based on a ISSCC paper. I am waiting to see what actually appears in products. thats just me LOL

Last edited:

Xebec

Well-known member

We know it'll be ~4Ghz Apple products in 2026:perhaps we should not judge an entire node based on a ISSCC paper. I am waiting to see what actual appears in products. thats just me LOL

(Follows the usual playbook)

Xebec

Well-known member

a 33% difference increase in frequency at iso voltage that is ridiculous difference

Another interpretation is Intel can do 4.2 GHz at less than 0.8V.

Even if we assume 0.8V, that means Intel needs 58% of the same power usage at 4.2 GHz as TSMC does. (f*V^2).

delong.height

Active member

It's probably ok to conclude now that if Intel does miss its schedule again, it will be the fault of the board this time. PG will definitely not take the hit.

Are those sizes raw memory cell array or overall area including peripheral circuits (decode/sense/drive/muxing)?

I seem to remember seeing elsewhere that these numbers weren't apples-to-apples, TSMC figure was net (including peripheral) and the others were gross (memory cell only), and that in fact TSMC was considerably higher density, but I could be mistaken...

siliconbruh999

Well-known member

Intel has decoders as well the tweet is a long thread that should provide the details for what you are looking for.Are those sizes raw memory cell array or overall area including peripheral circuits (decode/sense/drive/muxing)?

I seem to remember seeing elsewhere that these numbers weren't apples-to-apples, TSMC figure was net (including peripheral) and the others were gross (memory cell only), and that in fact TSMC was considerably higher density, but I could be mistaken...

Do you have the comparable figures for TSMC?Intel has decoders as well the tweet is a long thread that should provide the details for what you are looking for.

View attachment 2819

P.S. never going to join Twitter/X...

MKWVentures

Moderator

Pat made sure that Intel is very consistent hitting the schedule for announcing delays to new products. Discipline is important at Intel.It's probably ok to conclude now that if Intel does miss its schedule again, it will be the fault of the board this time. PG will definitely not take the hit.

[Quote stolen from a recently retired Intel employee]

Xebec

Well-known member

Even that is an improvement over BK's Intel 10nm updatesPat made sure that Intel is very consistent hitting the schedule for announcing delays to new products. Discipline is important at Intel.

[Quote stolen from a recently retired Intel employee]

saurabh8290s

New member

Intel claiming 18A is ready.

www.intel.com

www.intel.com

Intel 18A | See Our Biggest Process Innovation

See how the Intel 18A semiconductor manufacturing process is the foundation of the systems foundry for the AI era.

Very nice! What does "being ready" mean exactly?Intel claiming 18A is ready.

Intel 18A | See Our Biggest Process Innovation

See how the Intel 18A semiconductor manufacturing process is the foundation of the systems foundry for the AI era.www.intel.com

Intel claims 18A is "The earliest available sub-2nm advanced node manufactured in North America, offering a resilient supply alternative for customers." Reading b/w the lines, this seems to suggest that TSMC N2 is also "ready".

saurabh8290s

New member

I think it means that they are ready for external customer tapeout. They targeted H1 2025. I think they are on schedule till now.Very nice! What does "being ready" mean exactly?

Intel claims 18A is "The earliest available sub-2nm advanced node manufactured in North America, offering a resilient supply alternative for customers." Reading b/w the lines, this seems to suggest that TSMC N2 is also "ready".