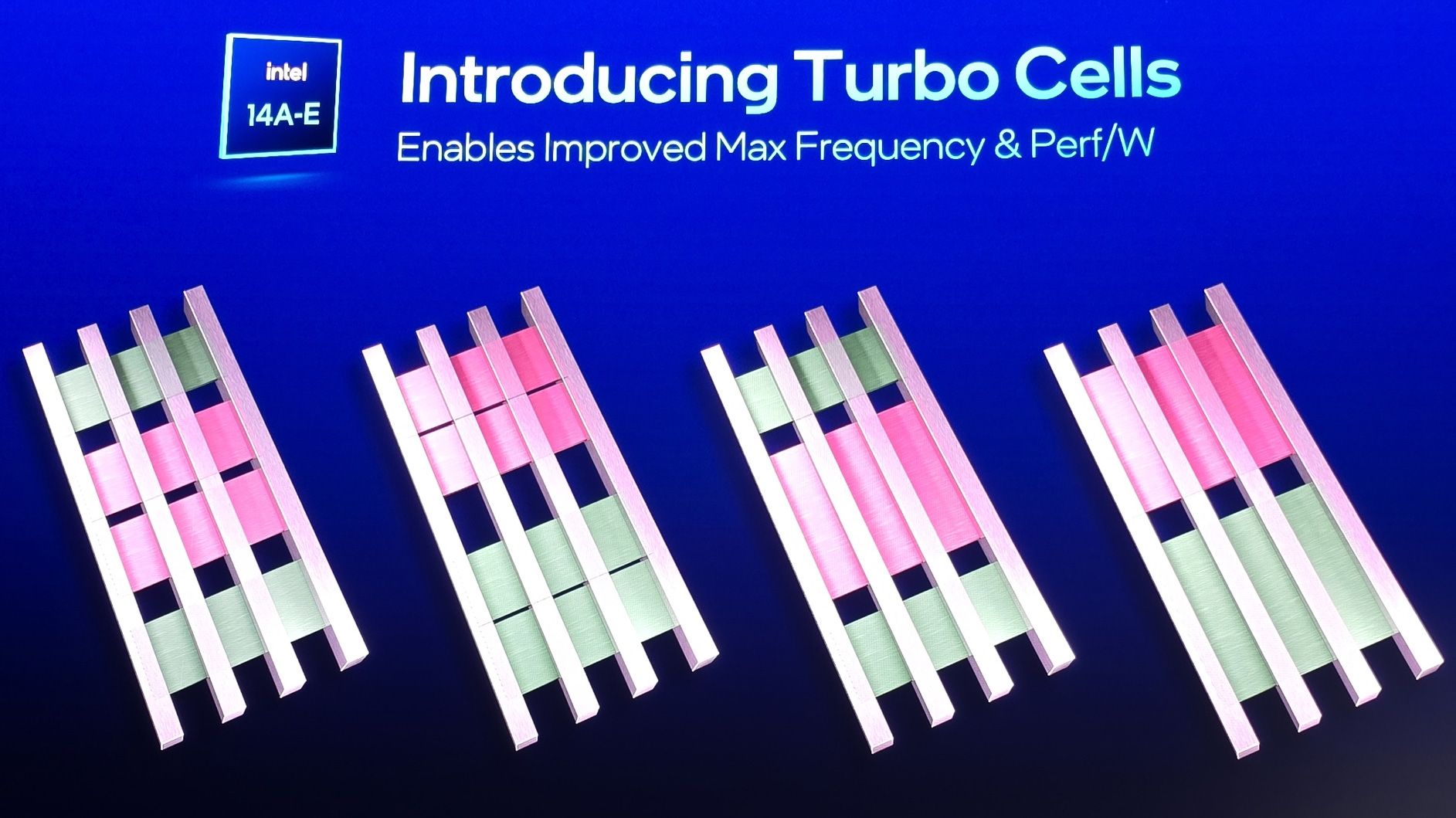

Btw I didn't hear a word about turbo cell is it similar to Nanoflex?

View attachment 3125

Intel details 14A performance and new 'Turbo Cells' that unlock maximum CPU and GPU frequency

I. Am. Speed.www.tomshardware.com

Short answer is yes, Intel's response to Nanoflex. You can mix high performance standard cells in with your standard or low power library. I do not remember cell height being mentioned but generally they are a few tracks taller (bigger transistors). Maybe 9 track versus 6 or 5 track? We used to have to choose between a high performance library versus a low power library or something in the middle. Now you can have a mix, tall cells for critical paths and smaller cells for better density/power.

TSMC has been showing N3 FinFlex benchmarks with Arm cores and they really are impressive. Nanoflex is for N2 but same principle. NanoFlex Pro is A14. Everything is on Youtube