At the recent Chiplet Summit, presentations, discussions and general participation could be broken down into a few broad categories. There were presentations of actual chiplet designs, either as building blocks or end products. There were presentations regarding design tools and methodologies to support and accelerate the new chiplet paradigm. In the enabling chiplet category, there were presentations on the standards that are helping to unify the market. And finally, there were presentations about hardware that integrates with chiplets to make the whole thing work.

Arteris is a company that fits into this last category, and Arteris was clearly present at the show with key technology that clears a road to the future. Let’s see how Arteris highlights a path to scalable multi-die systems at the Chiplet Summit.

The Presentation

The presentation was on Thursday afternoon of the event during a session that discussed new approaches to die-to-die interfaces entitled “Enabling Scalable Multi-Die Systems for AI, HPC, and Automotive ADAS”. The presentation was given by Ashley Stevens, who is director of product management and marketing at Arteris. Ashley is responsible for coherent NoCs and die-to-die interconnects. He has over 35 years of industry experience and previously held roles at Arm, SiFive and Acorn Computers. He holds 11 granted patents and has a degree in Computer Engineering from Queen Mary, University of London.

Ashley began by describing how the semiconductor industry is transitioning from traditional monolithic chips to chiplet-based multi-die architectures to meet the rapidly growing demands of artificial intelligence and high-performance computing. He explained that historically, improvements in semiconductor performance were driven by Moore’s Law, which doubled transistor density roughly every two years, although this is now slowing. However, AI workloads are expanding far faster than this pace, with compute demand increasing about every six months. Because monolithic chips are constrained by manufacturing reticle size, cost, and yield, the industry is increasingly adopting chiplet-based designs to continue scaling performance and system complexity.

Ashley explained that chiplets provide several advantages that make them attractive for next-generation systems. By dividing a large system into multiple smaller dies, designers can assemble chips that are larger and more powerful than a single die would allow. Smaller dies typically have higher manufacturing yield, which reduces cost. Chiplets also enable design reuse and product differentiation, allowing companies to create multiple product variants by combining different chiplets. This modular approach supports a broader portfolio of products and helps companies respond more quickly to changing market requirements across segments such as enterprise computing, communications, automotive, and consumer electronics.

He pointed out the further potential benefit of chiplet architectures is the eventual development of open chiplet ecosystems. He explained that in such ecosystems, chiplets from various vendors could interoperate on the same packaged device, enabling greater flexibility and innovation across the semiconductor industry. Today, most chiplet systems are still developed within closed environments by integrated chip vendors. However, the industry is moving toward standards-based interoperability, where chiplets and die-to-die interconnect technologies can work across multiple vendors and design environments. This shift could significantly accelerate innovation and broaden participation in complex semiconductor system design.

He also described how chiplet systems are evolving in complexity. Early implementations often used homogeneous chiplets, where multiple identical dies were connected in predefined topologies. Over time, systems are becoming increasingly heterogeneous, combining different types of chiplets such as CPUs, GPUs, AI accelerators, memory controllers, and specialized processing units. These heterogeneous systems may require more diverse die-to-die communication protocols and system architectures. In heterogeneous multi-die solutions, silicon processes can be optimized to meet the required functionality. For example, SRAM doesn’t scale to advanced logic processes, so using a more mature node for very large SRAMs is appropriate. Some I/O and analog/mixed signal designs are not viable on the most advanced logic processes and so can be implemented on a separate die. Ultimately, future chiplet-based systems may function as highly modular computing platforms built from interoperable components.

He went on to describe how advances in packaging technology are enabling these larger and more complex systems. In particular, 2.5D silicon interposer technology allows multiple dies to be connected within a single package using high-bandwidth interconnects. While individual dies are limited by reticle size during fabrication, interposers can host many chiplets together, effectively creating systems that are several times larger than a monolithic chip. Roadmaps presented in the slides show increasing interposer sizes over time, enabling progressively larger multi-die systems that support the growing computational demands of AI and data center workloads.

A central focus of the presentation was the Arteris multi-die interconnect solution, which extends network-on-chip (NoC) architectures across multiple chiplets. Arteris provides two main approaches. The FlexGen and FlexNoC technologies have been used by customers to support non-coherent die-to-die communication using standard protocols such as AMBA AXI and external physical interfaces like UCIe or PCIe. These solutions enable the efficient connection of chiplets while maintaining flexibility in system architecture. They are already being deployed by customers building multi-die systems.

For systems that require shared memory and cache coherence across chiplets, Arteris offers the Ncore multi-die coherent interconnect solution. Ncore enables the network-on-chip to seamlessly extend across multiple dies, enabling low-latency communication between processors and accelerators distributed across chiplets. The solution uses industry standard interface protocol AMBA CXS to interface to a third-party UCIe controller and PHY. This architecture allows designers to build large coherent systems in which chiplets behave as a single, unified, fully coherent system.

The Arteris Ncore multi-die solution supports up to 4 die-to-die links per chiplet and up to 4 chiplets per ‘Assembly’, meaning a collection of dies connected in a specific topology. The die-to-die links can be grouped together to increase bandwidth over a link or used to connect to multiple dies. To enable dies to be easily rotated to minimize routing on the interposer, Ncore supports port remapping, in which any physical die-to-die UCIe link can be mapped to any internal logical link. Pin-swapping (as opposed to port mapping) is also required, but is a standard feature of the UCIe PHY. The Arteris solution also supports ‘sub-assemblies’, the ability to remove dies from an assembly to make smaller devices. For example, a 4-die assembly can be reduced to 3, 2, or even 1 die and still operate fully, enabling manufacturers to quickly build a varied product portfolio.

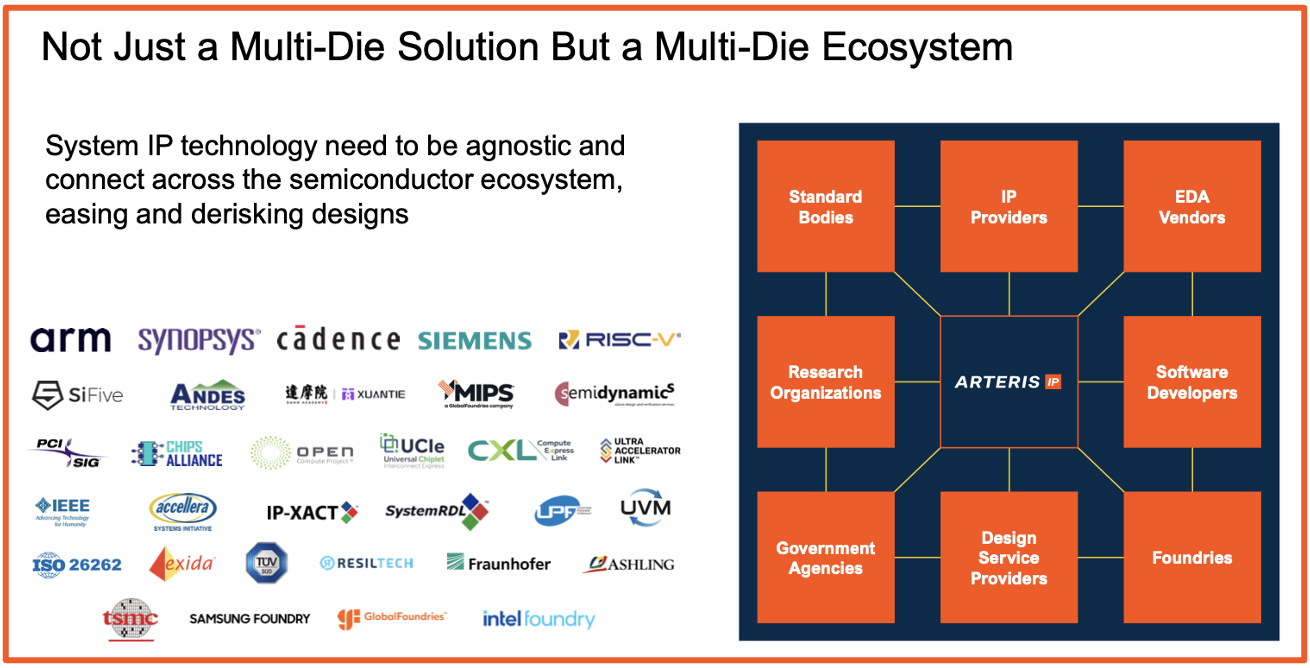

Ashley emphasized that the success of chiplet-based design depends on the broader semiconductor ecosystem. Challenges remain in areas such as interoperability, standardization, and verification of chiplets developed by different teams or vendors. The industry must develop common standards for protocols, address mapping, discovery, and verification methodologies. Collaboration among IP vendors, EDA tool providers, foundries, standards organizations, and design service providers will be essential to enable scalable chiplet ecosystems. By addressing these challenges, Arteris aims to support the next generation of AI-driven silicon systems and accelerate innovation in multi-die chip design.

The graphic below summarizes these points.

To Learn More

Arteris is well-known for its NoC technology, which provides a reliable fabric for integrating chiplet-based designs. If you plan to move in this direction, you should learn more about how Arteris can help de-risk your path. You can learn more about Arteris and chiplets here. And that’s how Arteris highlights a path to scalable multi-die systems at the Chiplet Summit.

Also Read:

The Next Hurdle AI Systems Must Clear

Arteris Smart NoC Automation: Accelerating AI-Ready SoC Design in the Era of Chiplets

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.