With the slowing down of Moore’s law , the industry as a whole has been working on various ways to maintain the rate of growth and advancements. A lot has been written up about various solutions being pursued to address specific aspects. The current era is being referred to by different names, SysMoore being one that Synopsys uses. Chairman and co-CEO of Synopsys, Aart de Geus coined this term as a shorthand way to describe the new era. One that blends Moore’s law driven advances with innovations that tackle systemic complexity. As per Synopsys’ website, “SysMoore is a descriptive term for state-of-the-art integrated circuit design, which combines the scale complexity of Moore’s law with the systemic complexity of hyper-convergent integration.”

Synopsys gave a presentation at DAC 2021 on the topic of delivering systemic innovation to power the era of SysMoore. The talk was given by Neeraj Kaul, VP of Engineering, Silicon Realization Group (SRG) at Synopsys. He starts by looking back at Moore’s Law era and spends the rest of his presentation focusing on the SysMoore era. He highlights new complexities and opportunities for new advances and what Synopsys is bringing out in terms of new technologies for this era. The following is a synthesis of the salient points I gathered from his talk. You can listen to Neeraj’s entire talk from the TechTalks track of DAC 2021 2021 virtual sessions.

View of an Evolving Landscape

Transformation is happening at a much faster rate than we have seen in the past few decades. The amount of compute power currently available is tremendous. At the same time, the amount of data being sensed, processed, transferred in petabytes, exabytes and zettabytes is requiring us to re-examine our way of computing. The number of design starts are accelerating at a rapid rate. This is placing tremendous pressure on the industry and calls for thinking of new ways of handling the complexity requirements and time pressure demands of the markets.

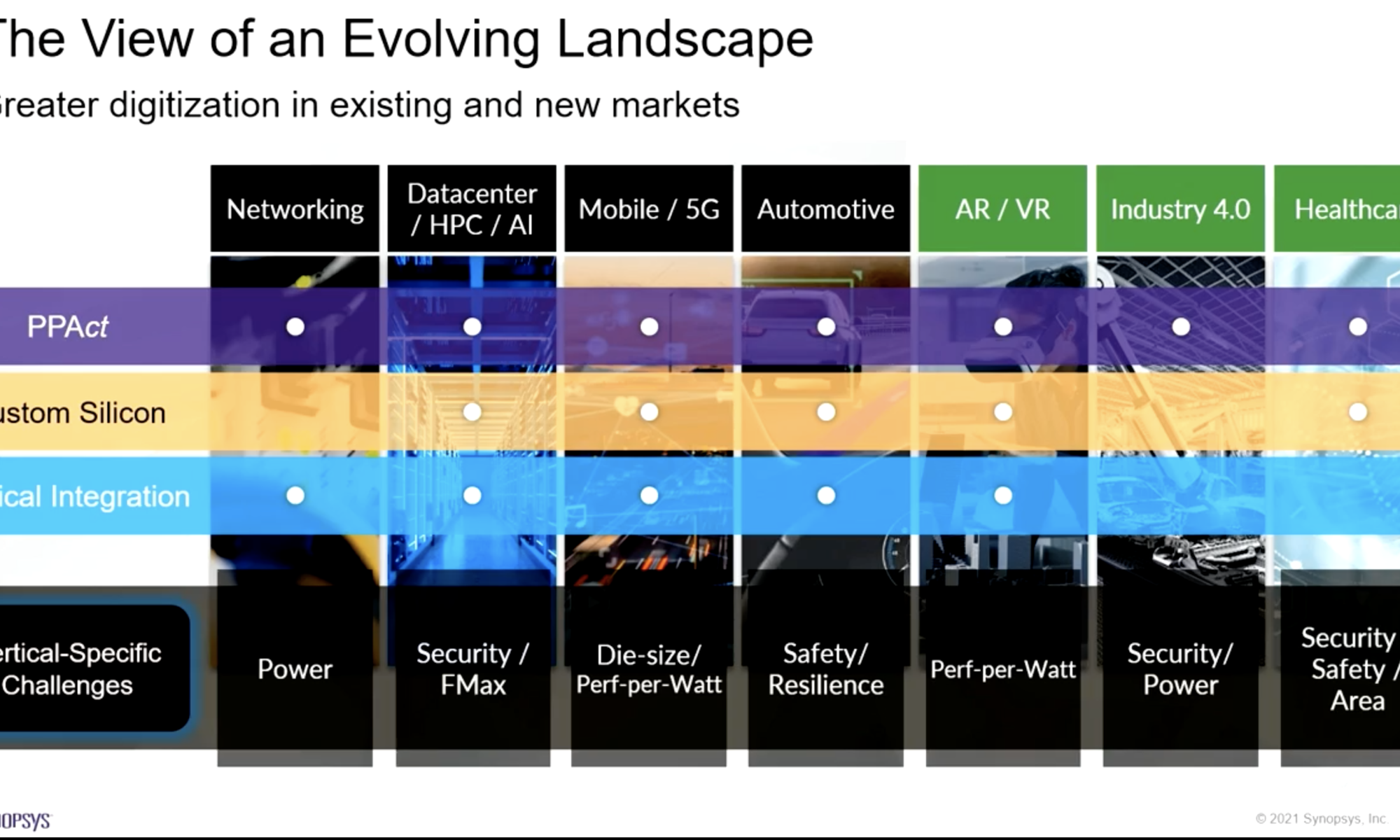

There are a number of vertical markets in this evolving landscape. Refer to Figure below. While the markets are vertical, there are some things all of them have in common. Those common things are the time-old performance, power and area (PPA) requirements and an increased pressure for cost and turnaround time to results. Together, these five things are termed by the acronym PPAct. Generic purpose chips cannot deliver to market/product expectations on PPAct metrics. The pressure is pushing customers to design custom silicon. Custom silicon initiative allows customers to look at the entire system all the way from software to silicon and optimize through vertical integration.

As if the PPAct pressures are not enough, SysMoore applications introduce Vertical-Specific challenges into the mix. For example, mean-time to failure, longevity of a chip, security, etc., become critically important when dealing with data center, automotive and healthcare markets.

The Waning of Moore’s Law Era

Moore’s Law had been delivering well over several decades. We got accustomed to seeing 2x improvements on all three aspects of the PPA metric, every two years or so. Last few years, we have seen a flattening of the Moore curve. PPA improvement is becoming difficult to achieve simply by moving from current process node to the next node. As we started entering the sub-7nm era, power and performance are not scaling at the same rate as Moore’s law has been delivering. We are seeing only 15% to 30% improvement moving from node to node. Power and performance are becoming bottlenecks, while the area scaling continues to deliver at 2x. But the market demand for power and performance improvements remains. The industry and the market have entered the SysMoore era.

Synopsys’ Approach to Powering the SysMoore Era

The SysMoore era requires innovations in many different areas in addition to moving from node to node. We need ways to deal with systemic complexities and continue to advance in the same way and same rate at which we were doing in the past. The systemic complexities are adding to the explosive demand on engineering resources, compute power needed and turnaround time expectations. We need techniques to improve overall productivity, so that we don’t need 2x-3x number of engineers to tackle the SysMoore era designs and systems.

Synopsys has identified six vectors as complexity/efficiency roadmap drivers to power the SysMoore Era.

Enabling domain-specific architectures

Support for domain-specific architectures is key to achieving customers’ PPAct metrics as these architectures help maximize performance and minimize power for each application. Synopsys’ Platform Architect and RTL Architect products are used by designers and architects to customize and optimize their systems and chips. Neeraj shared a customer example where they used the RTL Architect product to explore a larger design space and choose the right RTL architecture. The customer was able to achieve 5X faster TAT and 300MHz frequency boost for their product.

Scaling Challenge

Traditional tools/flow requires iterations, builds in pessimistic margins and delivers sub-par PPA results. 1D, 2D and diagonal placement rules and context-based timing and power all are crucial to consider up in the early stages of a design. The Fusion technology/platform from Synopsys is a hyperconverged system handling RTL to Tapeout with an integrated common database. The flow/platform is augmented with AI-driven Design-Space-Optimization (DSO) to achieve better results faster. And a comprehensive analytics platform completes the trifecta. This triple play of Fusion, DSO and Analytics platform enables customers to quickly and accurately identify root causes of issues. This in turn helps customers rapidly resolve the issues.

A customer example that Neeraj presented shows a 11% power reduction with just one engineer working on a high-performance GPU design. In the past, achieving comparable results would have consumed many engineers working on it for many months.

Robustness analysis for advanced-node variability

On-chip variation is a big issue these days as we move to finer and finer geometries. Synopsys PrimeShield analyzes robustness of a design for on-chip variation. It performs sensitivity analysis and fixes paths before silicon failure. The tool helps identify sensitive bottlenecks and improves resilience to IR drops. This analytical capability helps improve post-silicon robustness by detecting voltage slack paths and optimizing before tapeout. Voltage slack is a new metric to measure how resilient a design is to voltage variation. Neeraj shares a customer example where a 9% voltage slack improvement was achieved on a CPU core.

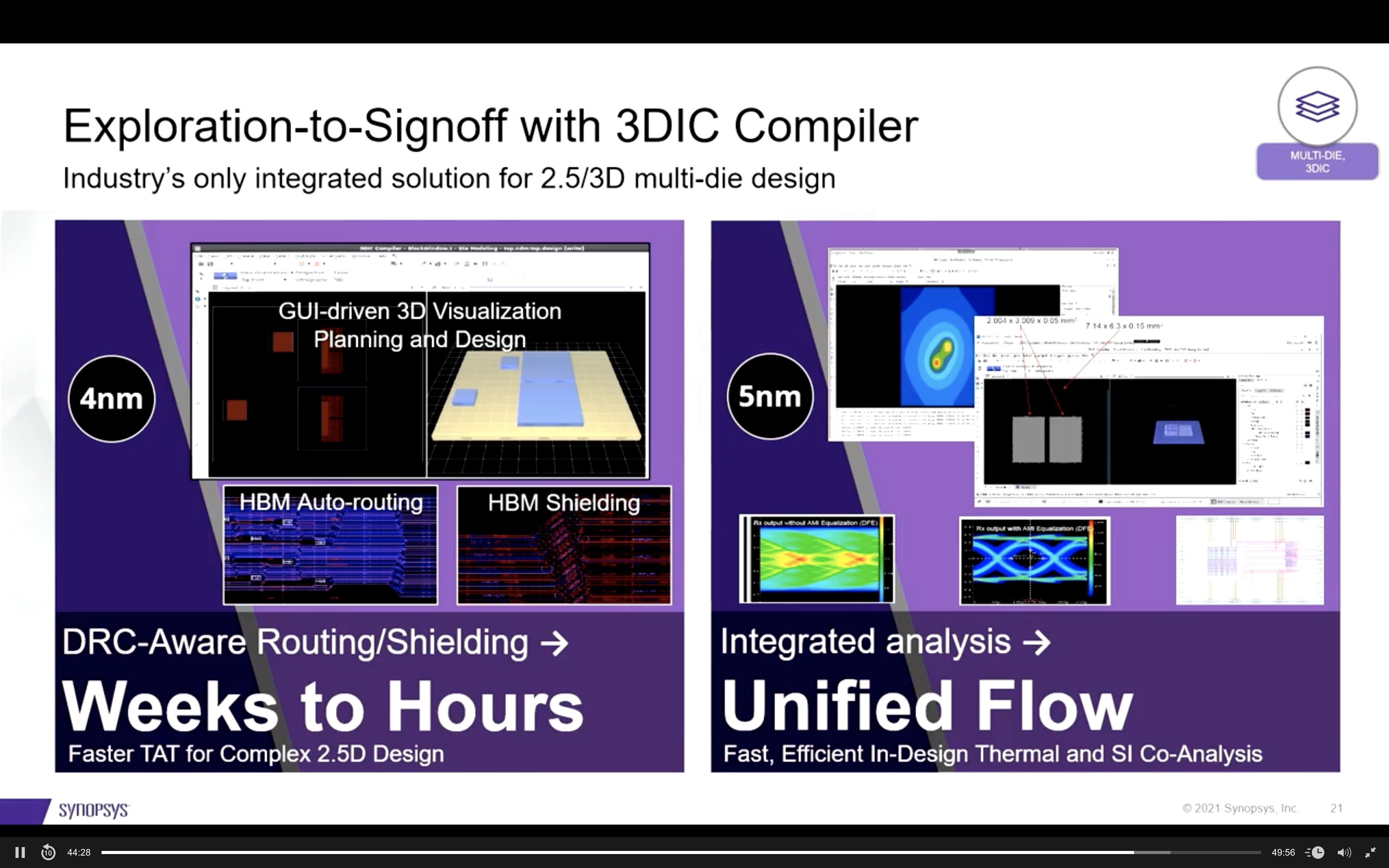

3DIC Compiler

Synopsys 3DIC compiler enables efficient integration of system-of-chips, aka chiplets leveraging 2.5/3D multi-die designs. It leverages the Fusion single data model and allows for fast exploration and pathfinding to accelerate design process. Auto die-to-die (D2D) routing, native DRC and DFT for design realization and validation are included. Together with signal integrity, power integrity, thermal and EMIR analysis, it assists designers in arriving at optimal PPA per sq.mm.

Summary

The fusion of tools over an integrated common database, the deployment of AI techniques to augment the tools and the provision of insightful analytics are key to powering the SysMoore era. Synopsys’s innovations are designed to address the PPAct, productivity, safety, security and resilience requirements of this era’s markets and applications.

Also Read:

Creative Applications of Formal at Intel

Synopsys Expands into Silicon Lifecycle Management

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.