Back in 1986, Synopsys started out with a synthesis product by name of SOCRATES, which stands for Synthesis andOptimization ofCombinatorial logic usingRule-basedAndTechnology independentExpertSystem. It is fair to say that not many designers know that was the birth name of what eventually turns out to be a very successful synthesis tool –Design Compiler. Over the last three decades, it has evolved to keep pace with the push and pull of Moore’s Law, advancements in process technologies, compute architecture shift and better software algorithms. Let’s replay how it has evolved over time.

Back in 1986, Synopsys started out with a synthesis product by name of SOCRATES, which stands for Synthesis andOptimization ofCombinatorial logic usingRule-basedAndTechnology independentExpertSystem. It is fair to say that not many designers know that was the birth name of what eventually turns out to be a very successful synthesis tool –Design Compiler. Over the last three decades, it has evolved to keep pace with the push and pull of Moore’s Law, advancements in process technologies, compute architecture shift and better software algorithms. Let’s replay how it has evolved over time.

Drivers to the Evolution

The first generation of Design Compiler (DC) took Boolean equations, optimized and minimized them and generated the combinatorial logic. Over time it has been revamped to handle more features such complex HDL constructs, pre-optimized building blocks (DesignWare IP), automatic DFT test-insertion and power related clock-gating among others. Its compile step also had gradually evolved from having only few options such as high, medium or low effort –to be more granular, as it accommodated increased designers awareness in optimizing more complex and higher performance logic. This includes the options to do compile_ultraand incremental compiles.

From methodology standpoint, DC interaction with the adjoining and downstream tools has been shaped by both the process-technology related geometrical scaling drive and satisfying designers automation needs. For example the use of wire load model was considered the norm during micrometer process node era. Designers who wished to push timing optimization further applied more area-centric, custom wire load models.

From methodology standpoint, DC interaction with the adjoining and downstream tools has been shaped by both the process-technology related geometrical scaling drive and satisfying designers automation needs. For example the use of wire load model was considered the norm during micrometer process node era. Designers who wished to push timing optimization further applied more area-centric, custom wire load models.

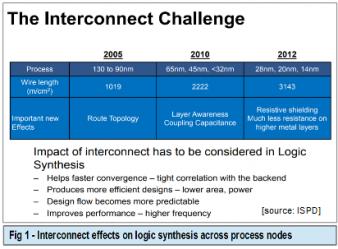

As wire scaling did not track well with device scaling in subsequent nanometer processes (as shown in figure 1), the lagging interconnect performance had disrupted the overall timing optimization results. TLU+ based RC modeling was then introduced to provide more accurate early wire estimation during synthesis and was embedded as part of DC-T or DC-Topographical.

While designers applied frequent synthesis cost-factor rebalancing to achieve an optimal QoR (Quality of Results), the slower interconnect had shifted top critical paths characteristic from gate dominant to more interconnect dominant, and caused a disconnect in assessing potential hot-spots (congested areas) in the design. This resulted in aggressive efforts made by the place and route tools in attempting to complete net connectivity with the available wire resources, and creating either routing congestion or scenic routes in the process. In order to account for such event, DC was once again enhanced to be ‘physically aware’ –DC-G or Design Compiler Graphical was rolled-out in 2011 to provide congestion prediction that was aligned with ICC place and route tool. Furthermore, deep advanced nodes, such as 10nm, 7nm and below, have also imposed the necessity of having accurate pre-route resistance estimation in synthesis step. DC-G was upgraded to handle such advanced nodes effects such as layer-aware optimization and via ladder.

The Next Generation Synthesis

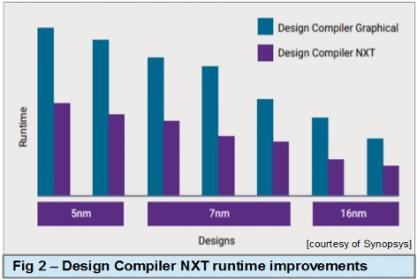

Early this month Synopsys released Design Compiler NXT, a new addition to the Design Compiler family of synthesis products. It addresses customer demand for a greater throughput and improved PPA (power, performance and area) as well as a tight correlation to physical implementation tools. It delivers 2X faster runtime, 5% better QoR for dynamic power, and a new cloud ready distributed processing engine.

“Design Compiler NXT built on Design Compiler Graphical leadership position with innovation enabling improved quality of results and designer productivity. Technology Innovations include fast and impactful optimization engines, cloud-ready distributed synthesis, more accurate RC estimation and new capabilities to support 5 nanometers and below,” stated Dr. Michael Jackson, Synopsys VP of Marketing and Business Development.

According to Abhijeet Chakraborty, Synopsys Group Director of R&D Design Group, Design Compiler NXT incorporates high-efficiency engines yielding half the runtime for compile and optimization operations. Design Compiler NXT distributed synthesis capabilities enables each distributed machine to optimize the design with full physical and timing contexts, which yields faster synthesis runtimes without sacrificing QoR.

“Design Compiler Graphical has been the trusted synthesis tool for our designs for many years and a key enabler to the development of our advanced SoCs and MCUs,” said Tatsuji Kagatani, Vice President, Shared R&D Division 2, Broad-based Solution Business Unit, at Renesas Electronics Corporation. “We are collaborating with Synopsys on the latest synthesis technologies in Design Compiler NXT and are looking forward to deploying them on our designs to help meet our ever-increasing pressure of time-to-market and higher QoR.”

Common Library, Models and Advanced Nodes Support

Design Compiler NXT also provides users benefit through a new support to common physical libraries (common library and block abstract models) with IC Compiler II. Often times, library updates introduced during the ongoing project development may introduce library inconsistencies between synthesis, place-and-route, and physically-aware signoff-driven ECO. It also continues to support Milkyway for full backwards compatibility, a plug-and-play, user interface and script compatible with existing Design Compiler Graphical. This enables a seamless transition for users.

New power driven mapping and structuring techniques, the addition of concurrent clock and data (CCD) optimizations deliver enhanced QoR. It has been redesigned to meet modeling needs of advanced process nodes, improved interconnect modeling, net topology and local density analysis engines that delivered tight correlation to IC Compiler II.

In summary, Design Compiler has been the industry leader for over 30 years and has delivered synthesis innovation in the area of test, power, data-path and physical synthesis. With this new addition once again Synopsys is raising the bar in evolving their RTL synthesis to enable SoC designs to target many emerging applications.

For more details on Design Compiler NXT, please check HERE

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.