There was a time when design goals were decided in the beginning, targeted on a particular technology node, design planning done for the same, and implementation done through point tools connected indesign flows customized according to the design. It’s no longer the case for modern SoC designs; there are multiple technology nodes to consider before planning for a design, a complete design system has to be in place with tools at all levels sharing design information as required, smart methodologies must be employed to gain best accuracy, and planning done at each stage for better QoR and faster design closure. While there is no relaxation in PPA (Power, Performance, and Area) optimization, in Synopsys’ terminology the design completion has to “shift-left” with fewer resources and shorter time.

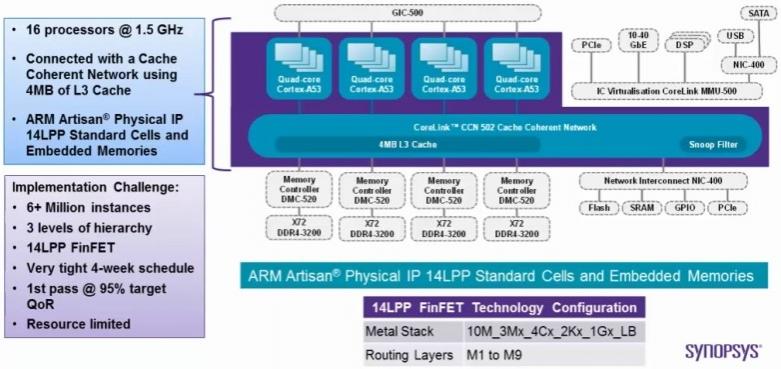

With that notion in my mind, when I came across the webinar from Synopsyson their Lynx Design System which was used to implement a network design with 16 ARM®Cortex®-A53cores and ARM Corelink[SUP]TM[/SUP] CCN-502on Samsung14LPP process, I happily attended it. Although new capabilities of IC Compiler II and Lynx Design System were introduced during this year’s DAC, I was interested to know more about these in a real design environment.

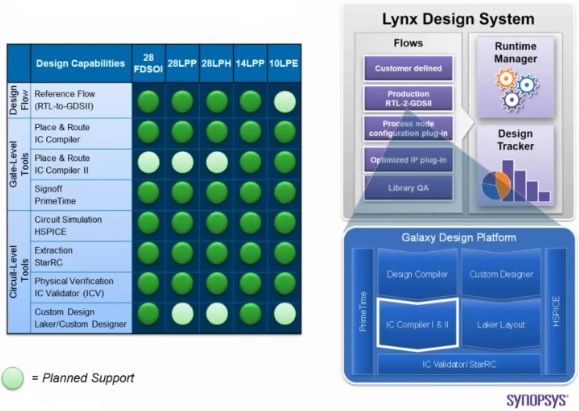

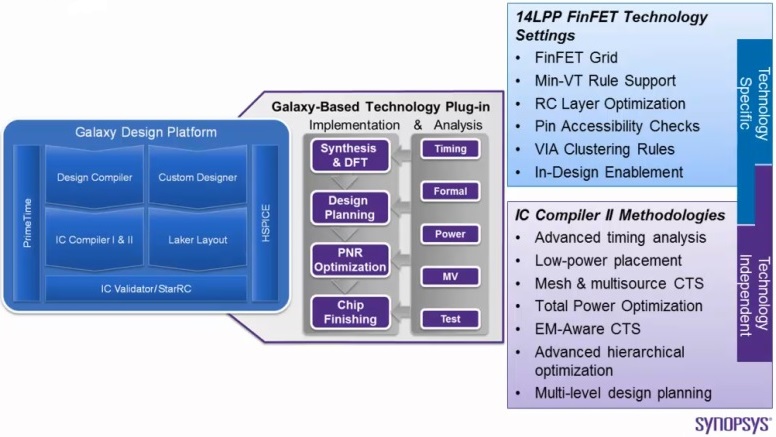

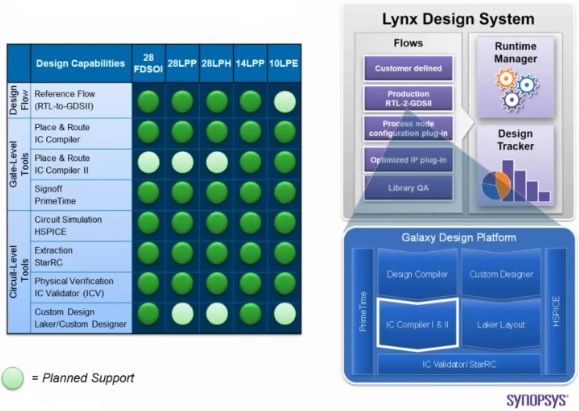

The Lynx Design System is ready for advanced technology nodes with leading foundries such as TSMC, Samsung, GLOBALFOUNDRIES, UMC, etc. Technology plug-ins are available to help customers quickly setup desired technology nodes. The design case in this webinar used the technology plug-in for Samsung’s 14nm technology node and Synposys’comprehensive RTL-to-GDS design flow in conjunction with ARM standard cell libraries. The platform already is being used by 50+ companies. The IC Compiler II P&R system is equipped with a versatile infrastructure to support multi-corner, multi-hierarchy, multi-mode, multi-voltage, and multi-view design; and powerful new floor-plan, clock-tree, timing and optimization engines. It provides up to a 10x increase in productivity with 5x faster implementation and half the iterations, all with better QoR.

Lynx employs a plug-in architecture where a technology independent layer of global methodologies can be combined with a technology specific layer as per foundry process requirements. The customized flow provides significant productivity for designers.

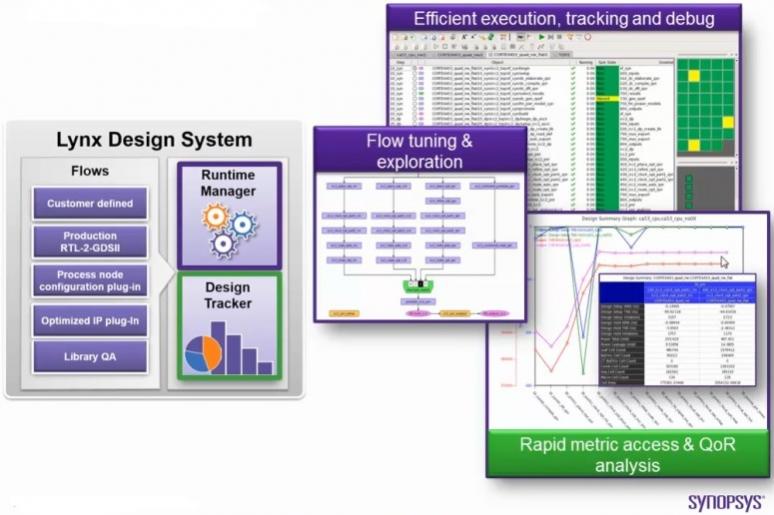

The system provides a flexible, user-friendly, iterative, and productivity-oriented flow where designers can explore for better alternatives and tune the flow accordingly with the help of a Runtime Manager. The Design Tracker provides progress reports in different forms including tables, graphs, and bar charts with links to original data files for faster access and analysis. There can be multiple tables, plots or bar charts in a report. Also proper data security is maintained for authorized access of files and reports. Separate reports can be obtained for designers’ and managers’ needs where a designer can dig into design specific attributes whereas a manager can check the project status. A good demo on design tracking is available in the webinar.

The QoR Viewer in the Lynx Design System provides many built-in reports for designers to analyze and ensure the best QoR for a design.

By using Lynx Design System designers could create an energy efficient processor subsystem reference implementation in just four weeks of time.

Frequencies of 1.44 GHz at ssa/0.72v/40c process corner and 1.7 GHz at tt/0.8v/25c process corner were obtained against planned 1.5GHz. The Lynx Design System provided best efficiency by combining fast hierarchical synthesis at pre-route stage and flat P&R implementation down the stream. The hierarchical synthesis employed Synopsys Physical Guidance (SPG) technique in Design Compiler Graphicaland flat P&R implementation leveraged the best capacity, runtime and QoR provided by IC Compiler II. The combined hierarchical synthesis and flat P&R approach reduces the overall TAT by 40% in this case.

Interactive design planning at the top level coupled with intelligent techniques such as module placement optimization and timing optimization through effort indicators on fly-lines makes the design more productive down the flow. The implementation flows at both synthesis and P&R stages can be tuned for best QoR and runtime. The Design Tracker can be used to review design summary, synthesis, clock-tree synthesis and other reports at various stages in both hierarchical and hybrid flows.

Chad Gamble at Synopsys has explained the system in more detail with good demos during the presentation. After a small registration step, the webinar of ~40 minutes can be attended HERE.

Pawan Kumar Fangaria

Founder & President at www.fangarias.com

Comments

There are no comments yet.

You must register or log in to view/post comments.