At the 2026 Synopsys Converge Event, Synopsys announced a broad set of new products and platform upgrades, with its hardware-assisted verification (HAV) announcement emerging as a key highlight within that lineup. A key aspect of this announcement was moving beyond a hardware centric model to a more scalable, programmable infrastructure that can continuously evolve through software updates. By positioning HAV in this way, Synopsys emphasized improvements in performance, automation, and system level validation needed to keep pace with the growing complexity of AI driven semiconductor designs. As AI systems scale in complexity and deployment accelerates, verification, has increasingly become a bottleneck to bringing new silicon to market. In that context, the shift to software-defined HAV represents a strategic response to one of the industry’s most pressing constraints.

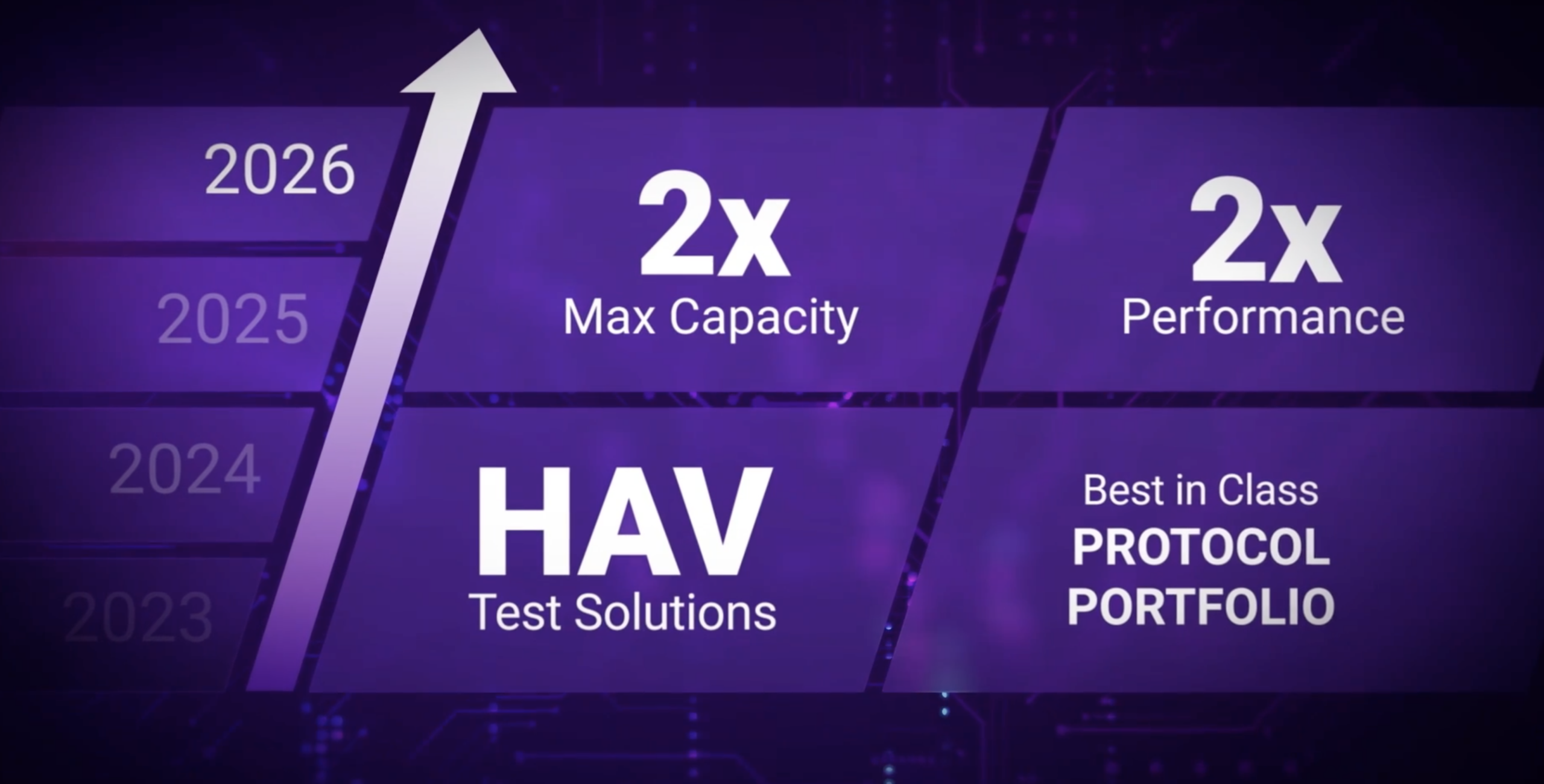

The announcement builds on the company’s 2025 introduction of next generation HAV hardware, including the Synopsys ZeBu-200 emulation platform and Synopsys HAPS-200 FPGA prototyping systems. Those platforms expanded capacity and performance for large system on chip designs. In 2026, Synopsys layered on top of that foundation with software-defined updates, along with automation capabilities, and new configurations such as the ZeBu-200 12 FPGA system and the HAPS-200 1 FPGA and 12 FPGA systems.

Verification Hits a Breaking Point

The backdrop to the announcement is a fundamental shift in semiconductor design. AI processors now integrate heterogeneous compute engines, massive memory bandwidth, and increasingly rely on multi die chiplet architectures. At the same time, the software stacks that run on these systems have grown just as complex.

Traditional RTL simulation, long the backbone of verification, cannot keep up with these demands at system scale. Running meaningful workloads can take weeks or months, making it impractical for validating full system behavior. The challenge is no longer validating blocks in isolation, but validating entire systems running real AI workloads, something conventional approaches cannot do within practical development timelines. Hardware assisted verification, using emulation and FPGA prototyping, has therefore emerged as a critical solution, enabling designs to run orders of magnitude faster and allowing software development to begin before silicon is available.

From Hardware Appliances to Software Defined Infrastructure

What distinguishes the 2026 announcement is a shift in how HAV platforms are conceptualized. Historically, systems like emulators and FPGA prototypes were treated as high performance but relatively fixed hardware appliances, with improvements tied primarily to new hardware generations.

Synopsys is now moving toward a software-defined HAV architecture, where platforms such as ZeBu Server 5, ZeBu-200, and HAPS-200 whose software layer dynamically manages resources, workloads, and debugging capabilities. This enables performance gains, such as up to two times improvements on ZeBu Server 5, to be delivered through software updates rather than requiring new hardware deployments.

This shift is critical because AI workloads, architectures, and software stacks are evolving faster than hardware refresh cycles. A hardware only model cannot keep pace with this rate of change. By contrast, software-defined HAV allows verification platforms to improve continuously, enabling teams to adapt to new AI workloads and system requirements without waiting for the next generation of hardware. The result is a more flexible and future proof verification environment.

Automation Moves into the Core of Verification

Another notable aspect of the announcement is the introduction of hardware-assisted test automation, signaling a shift toward more automated verification workflows. Rather than relying heavily on manually constructed tests, engineers can now run automated validation scenarios directly on HAV platforms.

These include complex system level checks such as cache coherency validation and subsystem stress testing across processor, memory, and IO architectures. In the 2026 announcement, Synopsys positions these not simply as automation features, but as hardware-assisted test solutions capable of exercising full processor subsystems under realistic workloads. By running automated coherency and subsystem validation directly on Synopsys HAV platforms, engineers can expose bugs that typically only appear under long running, highly concurrent AI workloads, conditions that are difficult or impractical to reproduce in traditional verification environments.

At AI scale, where subsystem interactions dominate system behavior, this shift from manually constructed tests to automated, workload driven validation becomes essential. The number of possible interactions across cores, caches, and memory systems is simply too large for manual approaches, making automation not just a productivity improvement, but a fundamental requirement for verifying modern AI processors.

Scaling for AI Scale Designs

Performance and capacity remain central to the HAV roadmap, and the 2026 announcement introduces meaningful gains in both areas. The ZeBu Server 5 sees up to a twofold increase in runtime performance, while modular configurations such as the ZeBu-200 12 FPGA and HAPS-200 12 FPGA systems enable similar scaling in capacity.

These improvements are critical for supporting AI chips that may incorporate tens of billions of gates, multiple compute domains, and complex interconnect structures. Faster compile times and enhanced debug capabilities further help teams manage these increasingly large verification workloads, reducing the time required to reach meaningful coverage. A customer quote substantiates this point. See below.

“As AI-driven systems become more complex, verification must scale just as quickly. Hardware-assisted verification is no longer optional. It is critical to meeting aggressive time-to-market goals and ensuring silicon readiness,” said Salil Raje, Senior Vice President and General Manager, Adaptive and Embedded Computing Group, AMD. “FPGA-based emulation and prototyping play a central role in that effort by accelerating system bring-up and enabling earlier software development. Our collaboration with Synopsys reflects that focus. Through joint optimization of Synopsys ZeBu with the AMD Vivado™ software stack, and by leveraging AMD EPYC™ processors for compute acceleration, we are reducing compile times and helping customers move to accurate system models faster.”

Flexible Configurations for a Broader Range of Use Cases

Alongside performance improvements, Synopsys is expanding the flexibility of its HAV offerings. The introduction of configurations such as the HAPS-200 1 FPGA desktop system provides an entry point for IP level validation and early software development, while larger configurations like the HAPS-200 12 FPGA and ZeBu-200 12 FPGA systems scale to full system verification.

This range of configurations allows design teams to align their verification infrastructure more closely with specific project needs, supporting a continuum from early stage validation to full system workload execution.

Expanding the Scope of What Can Be Verified

The 2026 HAV enhancements also broaden the scope of verification itself. New support for real number modeling (RNM) allows analog behavior to be approximated within digital verification flows, while fault emulation capabilities address the needs of safety critical applications.

These additions reflect a shift toward full system validation, where digital logic, analog effects, and software interactions must all be considered together. As semiconductor designs become more heterogeneous, this expanded coverage is essential for accurately validating real world AI systems rather than simplified models.

Summary

The Synopsys Converge Event HAV Announcement reflects a broader industry transition. As AI drives exponential growth in chip complexity, verification must evolve from a collection of tools into a scalable, software driven platform.

The significance of software defined HAV lies in its role in enabling AI proliferation itself. As AI hardware becomes more complex and deployment cycles accelerate, the ability to verify systems quickly and at scale determines how fast innovation can reach the market. By removing verification as a limiting factor, through continuous performance improvements, automation, and system level validation, Synopsys is positioning HAV not just as a tool, but as a critical enabler of the AI ecosystem.

Read the entire HAV announcement here.

Learn more at Synopsys.com/HAV

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.