The semiconductor industry has experienced rapid advancements in recent years, particularly with the increasing demand for high-performance computing, artificial intelligence, and advanced automotive systems. Traditional single-die chip designs are often unable to meet modern PPA requirements. As a result, engineers have turned to multi-die architectures, where multiple smaller dies are integrated within a single package. While this approach improves scalability and performance, it also introduces new challenges, especially in interconnect planning. One of the most critical aspects of multi-die integration is the efficient planning of bumps and TSVs that enable communication between different dies.

In multi-die designs, interconnectivity between chips is achieved through microbumps or hybrid bonding pads placed on the surfaces of dies. These bumps act as electrical connection points between dies, interposers, or substrates. Modern designs may require hundreds of thousands or even millions of such connections. As the number of dies and interconnects increases, the complexity of planning and managing these connections also rises dramatically. According to the provided white paper, improper bump planning can negatively affect routability, routing quality, and overall design efficiency.

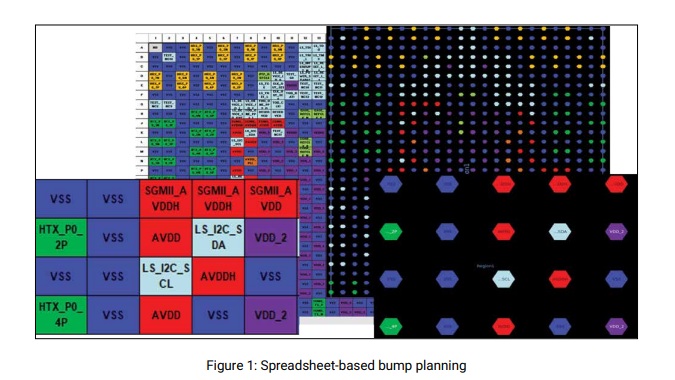

Traditionally, bump planning was done manually using simple graphical tools such as spreadsheets or diagram software. While this approach worked for earlier single-die flip-chip designs that contained only a few thousand connections, it is no longer practical for today’s large-scale multi-die systems. Manual planning is time-consuming and highly prone to human error. Furthermore, any modification to the bump layout of one die often requires corresponding changes in other dies or the package design. If these updates are not properly synchronized, significant design errors may occur later in the development cycle.

To address these challenges, modern EDA tools provide automated bump planning capabilities. These tools allow designers to define bump regions, which are rectangular or irregular areas on a die where bumps are placed. Within each region, bumps can follow specific patterns based on constraints such as pitch, spacing, and alignment. Once these patterns are defined, the software can automatically generate thousands of bumps quickly and accurately. If the region size or design constraints change, the bump layout automatically updates, saving designers significant time and effort.

Another key aspect of bump planning is signal assignment. Each bump must be connected to a specific signal, power line, or ground network. Designers may assign signals manually or use automated algorithms that optimize placement based on factors such as wire length and routing efficiency. Automatic signal assignment can analyze the entire multi-die system and determine the best possible mapping of signals to bumps, improving overall performance and reducing design complexity.

In addition to bump planning, designers must carefully plan through-silicon vias. TSVs are vertical electrical connections that pass through a silicon die, allowing signals and power to travel from the backside of the die to the frontside routing layers. TSVs are particularly important in 3D stacked chip designs where multiple dies are stacked vertically. However, TSVs are relatively large structures and require significant spacing and keep-out zones to avoid damaging nearby circuitry. Poor TSV placement can reduce the usable area for logic cells and negatively affect timing performance. Therefore, careful planning is necessary to ensure optimal TSV placement without compromising chip functionality.

Modern design platforms integrate bump and TSV planning into a unified workflow. This allows engineers to visualize connections in both two-dimensional and three-dimensional views, track engineering changes, and perform automated design rule checks. By detecting alignment errors, missing connections, or signal mismatches early in the design process, these tools help prevent costly mistakes during later stages of manufacturing.

Bottom line: Efficient bump and TSV planning plays a crucial role in the success of multi-die semiconductor designs. As chip architectures become more complex, manual planning methods are no longer sufficient. Automated design tools and structured planning methodologies enable engineers to manage millions of connections, maintain design accuracy, and accelerate time-to-market. With the continued growth of advanced technologies such as AI and high-performance computing, effective interconnect planning will remain a fundamental requirement in modern semiconductor design.

Also Read:

Reducing Risk Early: Multi-Die Design Feasibility Exploration

Building the Interconnect Foundation: Bump and TSV Planning for Multi-Die Systems

How Customized Foundation IP Is Redefining Power Efficiency and Semiconductor ROI

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.