The big three EDA companies all have Custom IC and AMS tool flows as shown in the following comparison table:

[TABLE] style=”width: 500px”

|-

|

| Synopsys

| Cadence

| Mentor

|-

| Schematic / Layout

| Custom Designer SE

Custom Designer LE

| Virtuoso Schematic Editor

Virtuoso Layout

| Pyxis Schematic

Pyxis Layout

|-

| SPICE Circuit Simulation

| HSPICE

| Spectre

| Eldo Classic

Eldo Premier

|-

| Fast SPICE

| CustomSim

| UltraSim

| ADiT

|-

| Waveform Viewer

| Custom WaveView

| Virtuoso Visualization

| EZ Wave

|-

| AMS Simulation

| CustomExplorer Ultra

| Virtuoso AMS Designer

| Questa ADMS

|-

| Analysis Environment

| Custom Explorer

| Analog Design Environment

| ICanalyst

|-

| DRC / LVS

| IC Validator

| Assura

| Calibre nmDRC

Calibre nmLVS

|-

| Parasitic Extraction

| StarRC

| QRC

| Calibre xRC

|-

| Digital P&R

| IC Compiler

| NanoRoute

| Olympus-SoC

Calibre InRoute

|-

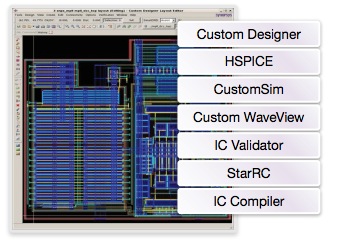

I wanted to learn more about the Synopsys tools so I read their recent White Paper: Custom and Mixed-Signal Design Solution.

From a market-share viewpoint the strengths of each EDA vendor are probably:

- Synopsys

- SPICE

- Digital P&R tools

- Cadence

- Schematic/Layout

- P&R tools

- Mentor

- DRC/LVS

- Parasitic Extraction

- AMS Simulation

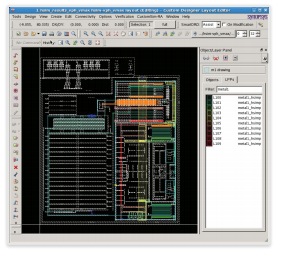

Schematic Entry and Layout Editing

Schematic entry and layout editing with Customer Designer SE and LE are relatively new EDA tools for Synopsys, and they use the OpenAccess database based on Si2 standards, and work with interoperable PDKs (Process Design Kits) – so you aren’t limited to Skill-based Pcells from Cadence. I’m still waiting to hear about the merged product roadmap after the acquisition of: Magma, SpringSoft, Ciranova; here’s a blog devoted to the topic.

Design-Rule-Driven Layout

At the 45nm node and below the layout rules have gotten so complex that you can iterate way too many times between your IC layout and DRC tools to get a clean layout, so with SmartDRD you can see DRC violations while doing interactive layout at the cell and block levels, shortening the number of times you need to run DRC in batch.

Digital P&R + Custom Layout

IC Compiler and Custom Designer work together using the same OA database, so no translations or importing steps are necessary.

SPICE and FastSPICE

Synopsys now owns the most circuit simulators out there after acquiring tools from: Magma, Nassda, Avant!. You can even simulate effects like:

- Electromigration (EM)

- IR-drop

- Static and dynamic checks

- MOS aging

Violations can be viewing in Customer Designer LE.

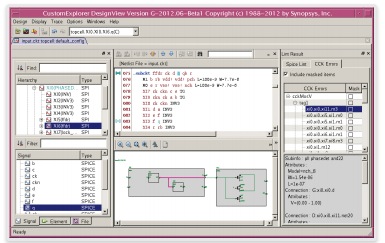

AMS Simulation

The transistor-level simulator CustomSim can co-simulate with the HDL simulator VCS, so you can mix and match language-based verification with transistor-level.

DRC / LVS / Extraction

Synopsys has tools for all three categories: DRC / LVS (IC Validator), Extraction (StarRC). Useful debug features like cross-probing between DRC / LVS results and the schematic or layout make life easier for physical verification engineers.

Eating Your Own Dog Food

In EDA this means using your software like an end-customer, so for Synopsys that means that their Analog IP group uses the complete flow of Synopsys tools listed in this blog to design the following:

Conclusion

Synopsys has developed and acquired enough EDA tools to create a complete tool flow for custom IC and AMS design. You can use all their tools together, or mix-and-match with other EDA vendor tools that use the OpenAccess database or de-facto standards (SPICE, iPDK, Verilog, Verilog-AMS, VHDL).

Comments

8 Replies to “Custom IC and AMS Tool Flow with Synopsys”

You must register or log in to view/post comments.