Will the launch of ARC based complete sound system IP by Synopsys ring the bell for the opening of a new IP market segment, the “Subsystem IP”? If you look at the IP market evolution, starting from standard cell libraries and memory compiler offering in the 1990’s, moving to commodity functions like UART or I2C in the late 1990’s to finally come to complexes functions offer in the 2000’s, the long list of standard based PCI, PCIe, USB 2.0, SATA and more, and if you start brainstorming, you will likely think that subsystem IP should be the next step. Your customers, the SoC integrators, have to fill IC with more and more function, the technology make it possible (think 40 or 28nm) and their customer ask for it. But the time to market (TTM) pressure, especially in market like wireless or consumer electronic, is so strong that the design team has to integrate more functions, in a technology more difficult to manage, that the “lego” solution (building a complete system by integrating – not designing- various subsystems) looks very attractive. Then, you think that subsystem IP is the ideal solution!

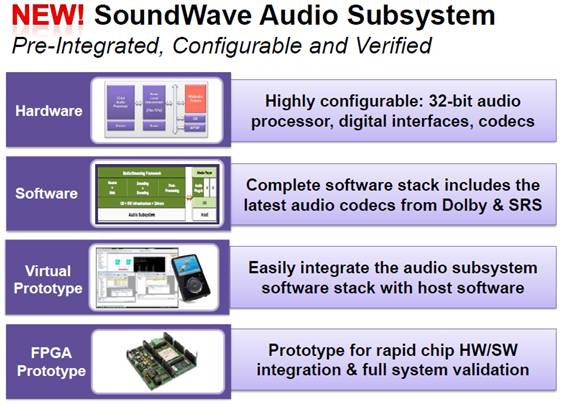

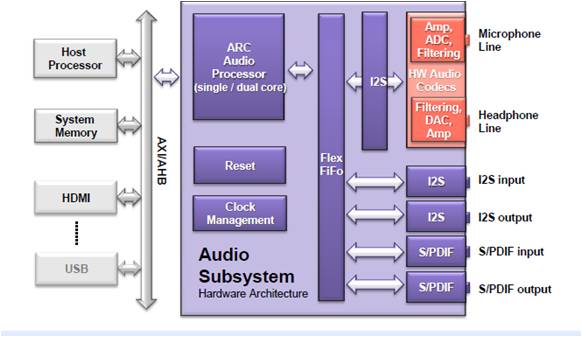

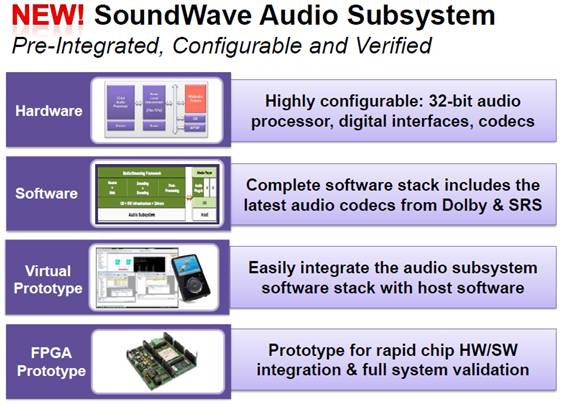

Synopsys offering of a sound subsystem IP is based on a complete solution: H/W, S/W, FPGA and Virtual prototyping availability. The hardware piece is articulated around a single or dual core ARC Audio Processor, highly configurable, and this is an important point, as SoC integrators always need to differentiate. If they want to provide an ultra low power solution, they will implement the solution running at 10 MHz frequency, when the 800 MHz solution will allow for performance differentiation. As well, a SoC integrator will decide to implement a very low footprint (0.2 sq mm in 40nm) version, if the goal is to release a low cost, low area SoC. But, in both case, ARC based subsystem IP, will be a complete, drop-in solution.

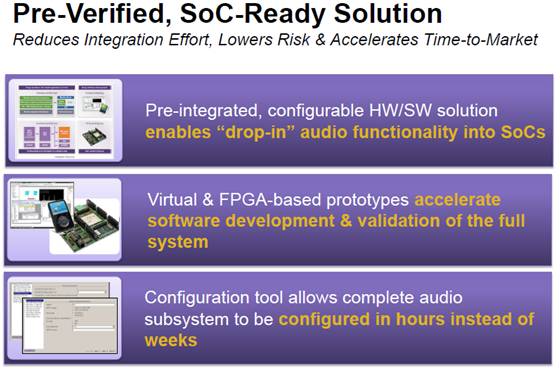

Because the market segments targeted are CE or Wireless, with applications like Set-Top-Box (STB), HDTV, handset or smartphone and multimedia, all of these requiring to provide sound capabilities (which can be pretty advanced like surround sound or multi-channel), but for which the sound features are not the core competencies of the chip maker, benefiting for a drop-in solution can make sense to complete the SoC integration on line with the TTM requirement. In other words, the Subsystem IP provider is not in competition with the SoC design team. The sound system is one of the features that the SoC needs to support, but not the most important feature of the SoC you are designing. Adopting such a drop-in solution accelerates TTM, does not compete with the design team core competencies (avoid NIH syndrome) and is a way to minimize risk: you integrates a pre-verified function.

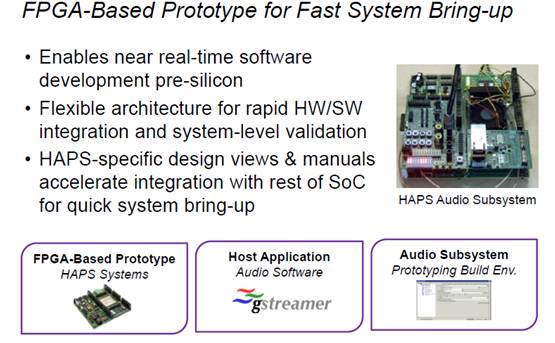

When designing a SoC for smartphone or STB application, you can’t afford taking the risk of a re-spin of the chip, because of the TTM pressure, using a pre-verified solution is one of your key requirement (even if it’s not always possible to do so). Offering a pre-integrated, pre-verified and still configurable sound subsystem IP is a good way to minimize the risk associated with this part of the design. Again because of the TTM pressure, you will need to develop the software in parallel with the SoC development and prepare for the validation of the full system as soon as possible (it’s not unusual to spend one year or more to run the validation of complexes application processors like OMAP5 or Snapdragon). FPGA based prototypes (HAPS based hardware prototyping) will allow to accelerate software development, and virtual prototyping to speed up the complete system validation phase, so you don’t need to wait for SoC prototypes release to start working on the SoC validation.

The semiconductor industry is a place where creativity is welcomed, as soon as creative thinking will allow making more money. It’s an industry where some “crazy” ideas like Microprocessor concept have leaded to create huge market starting from scratch, and also an industry where brilliant ideas like the Transputer (a pioneering microprocessor architecture of the 1980s, featuring integrated memory and serial communication links, intended for parallel computing, designed and produced by Inmos) or closer to us, the concept of an ASIC platform, pre-integrating multiple functions as well as field programmable blocks (FPGA areas), have finally failed. Subsystem IP is a brilliant idea. Will this concept meet the market demand? I honestly don’t know the answer, but that I can say is that Synopsys has tried to bring a complete solution, based on H/W, S/W and prototype offering, increasing the likelihood of success.

From Eric Estevefrom IPnest

Share this post via:

Comments

0 Replies to “Does Subsystem IP will finally find a market? ARC based sound subsystem IP is on track…”

You must register or log in to view/post comments.