The big three in EDA are well-know for offering AMS and RF IC design flows, but today you also have alternative EDA vendors available that have capable tools, yet are lessor known. This blog will present an overview of the AMS and RF IC design flowoffered by Silvaco, an EDA company with a strong history in TCAD tools like Utmost IV for device characterization and SPICE modeling.

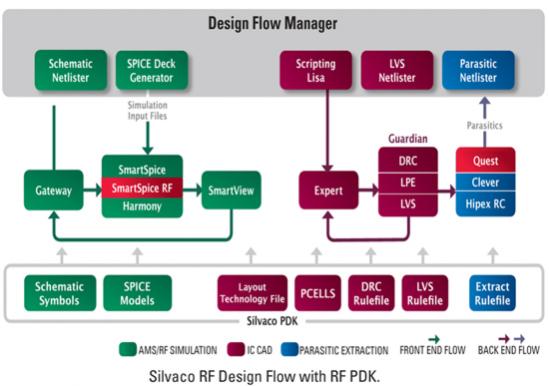

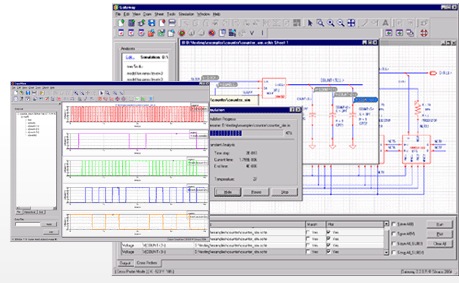

AMS design can begin either from a bottom-up approach using transistor level schematics, or from the top-down with a modeling language like Verilog-A. There’s even an approach where you use both bottom-up and top-down, then meet in the middle. For the bottom-up approach you want a schematic capture tool to enter your design topology, launch SPICE circuit simulations, then view the results with a waveform tool. The Silvaco schematic capture tool is called Gateway and it’s bundled along with a waveform viewer.

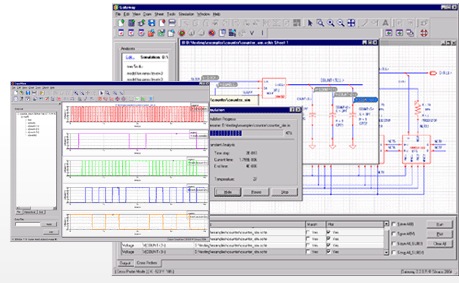

The GUI of Gateway has a standard Microsoft look, so it’s easy to learn and use. You can create multiple views, multiple sheets and of course, hierarchical designs. They even have something like the free Adobe reader for their schematics called GatewayViews – now when was the last time an EDA vendor offered you something of value for free? From the schematic GUI you can launch their SPICE circuit simulator called SmartSpice. If you prefer HSPICE for circuit simulation, that netlist format is also supported. Any legacy schematics that you need for design re-use can be imported with EDIF 2 0 0.

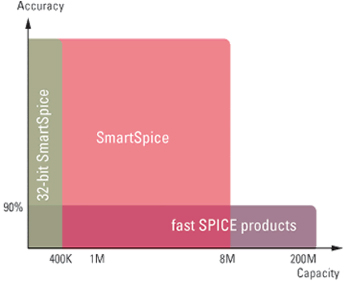

The SmartSpice circuit simulator has a capacity up to 8M elements and the accuracy is correlated against silicon. You can read in netlists from HSPICE or Spectre simulators and even re-use the models, analysis features and compare results to get convinced that SmartSpice is trustworthy. Analog behavioral modeling is supported with the Verilog-A language, and for reliability analysis you can simulate Single Event Effects (SEE).

On the RF simulation side their product is called SmartSpice RF and it has both frequency and time-domain circuit simulation. With this tool you can simulate GHz range RF ICs with: harmonic distortion, intermodulation products, gains, noise and even oscillator phase noise in non-linear circuits from a SPICE netlist. The design flow for RF design is similar to analog IC design with Silvaco tools:

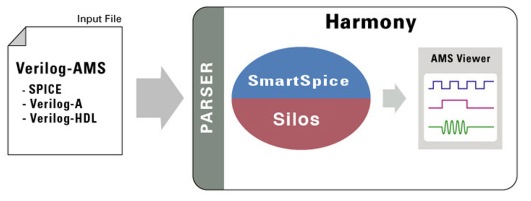

For mixed-signal simulation there is a single-kernel AMS circuit simulator called Harmony that uses SmartSpice for analog and Silos for digital blocks. Harmony does support the Accellera 2.2 standard for Verilog-AMS and Verilog-A, plus the IEEE 1364-2001 standard for the Verilog PLI. There’s a single parser that reads in both Verilog and SPICE syntaxes, and a single waveform viewer for analog and digital signals.

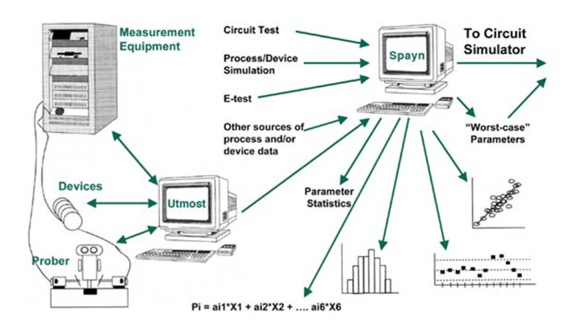

Analog designers often want to analyze a netlist to see how it behaves as model parameters are affected by process variations. The statistical parameter and yield analysis tool is called Spayn, and it can auto-generate worst-case and corner SPICE models. Engineers involved with characterization, process control and analysis would use the Spayn tool.

Summary

Well, there you have it, the 30,000 foot view on what Silvaco has to offer AMS and RF IC designers in terms of a complete EDA tool flow. You won’t find Silvaco at DAC in June, however you will see them at the CSW2014(Compound Semiconductor Week) in France on May 11-15, and at the Workshop on Compact Modeling in Washington, D.C. from June 15-19.

lang: en_US

Share this post via:

![SILVACO 051525 Webinar 400x400 v2[62]](https://semiwiki.com/wp-content/uploads/2025/04/SILVACO_051525_Webinar_400x400_v262.jpg)

Comments

There are no comments yet.

You must register or log in to view/post comments.