By Niranjan Sitapure

Artificial intelligence (AI) is reshaping industries worldwide. Consumer-grade AI solutions are getting significant attention in the media for their creativity, speed, and accessibility—from ChatGPT and Meta’s AI app to Gemini for image creation, Sora for video, Sona for music, and Perplexity for web search.

However, adapting these impressive models for high-stakes engineering applications, such as semiconductor chip design, manufacturing, and robotics, is much more complex. In these fields, model results that are incorrect, fabricated (hallucinations), or inconsistent are unacceptable. In consumer AI, a mistake might lead to a funny answer. In chip design, it can cost millions during tapeout and manufacturing. That’s why the EDA industry needs a more industrial-grade AI approach.

Consumer-grade AI versus industrial-grade AI

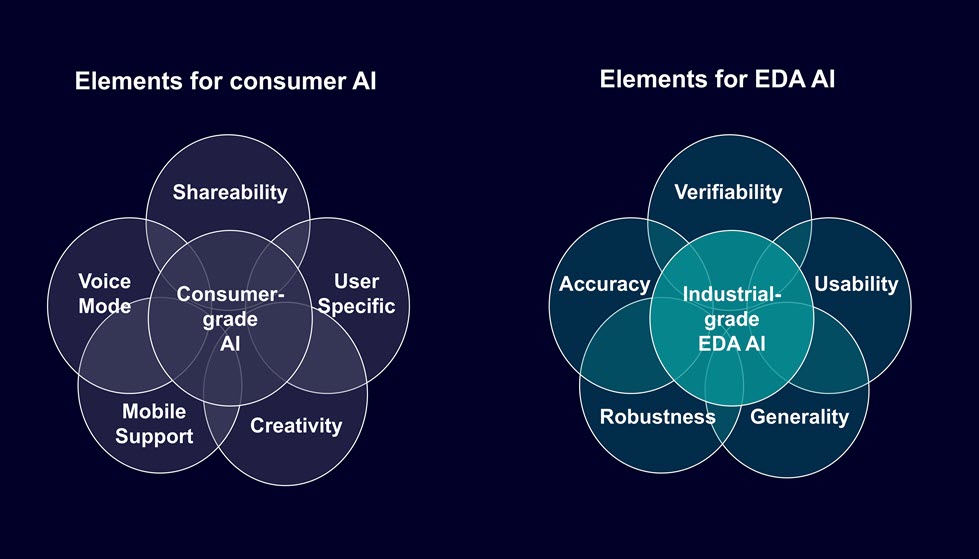

To understand this challenge, let’s first define the key characteristics of consumer-grade AI and see how they differ from the requirements for industrial-grade AI.

Consumer-grade AI is often optimized for:

- Creativity: Prioritizing the generation of novel ideas, text, and imagery, even when the results are not perfectly factual or precise.

- Mobile support: Emphasizing access and ease of use on smartphones and other portable devices.

- User-specificity and personalization: Adapting its style, recommendations, and memory to an individual’s personal history and stated preferences.

- Shareability: Integrating tools to quickly post, link, or export generated content to social media or messaging platforms.

- Voice mode: Enabling hands-free operation through spoken commands and audio responses for maximum convenience.

These principles are fundamentally different from the characteristics required for industrial-grade AI, which are based on the following:

- Accuracy: Ensuring all outputs are quantitatively correct and conform to strict physical laws and engineering constraints, where even a tiny error can be critical.

- Verifiability: Providing transparent, traceable decision-making paths so engineers can audit precisely how and why the AI arrived at a specific result.

- Robustness: Maintaining high performance, reliability, and consistency even when faced with novel, noisy, or incomplete data sets.

- Generalizability: Successfully applying insights and models trained in one design problem to new, unseen engineering problems.

- Usability: Seamless integration with established computer-aided design (CAD) and computer-aided engineering (CAE) software tools and engineering workflows, rather than functioning as a separate, standalone app, while also not requiring extensive training for the engineers to utilize these AI solutions.

AI for the high stakes of chip design

Now that we understand the key differences between the two paradigms, let’s explore why industrial-grade AI is necessary for the electronic design automation (EDA) tools that power chip design.

Firstly, accuracy is paramount. Every step in the chip design process, from the initial schematic to the final tapeout, demands absolute precision. A single error could substantially harm chip production or critical industrial processes, resulting in significant financial and operational losses in wasted manufacturing costs, complete chip failure, or costly product recalls. That’s high stakes risk the industry simply must avoid.

Secondly, robustness and reproducibility are critical. Today’s general-purpose LLMs are probabilistic models, meaning they may not guarantee the exact same output every time. This variability is problematic for engineering. If a general-purpose LLM is used for a precise task such as RTL generation or high-level synthesis (HLS), it might struggle to achieve complete reproducibility. This could make it difficult to replicate a specific design block or apply the same IP block consistently in a new chip design, creating significant challenges for verification and manufacturing.

Thirdly, verifiability and traceability are essential. Engineers can’t rely on a “black box” that just gives an answer. They need to understand how the AI made its decisions. For example, during placement and routing, an AI might analyze thousands of potential layouts. A verifiable system would log into these different options and the trade-offs associated with them. This allows the chip designer to trace back and see why one layout achieved better power, performance and area (PPA) than another, enabling them to trust and validate the final design.

Examples of AI in EDA

A clear example of these industrial-grade principles in action is seen in Siemens’ Solido Design Environment software. It uses Adaptive and Additive AI technologies to validate designs and IPs through Monte Carlo simulations for mixed-signal designs and custom ICs. This provides orders-of-magnitude speedup for complex tasks, such as variation-aware analysis. These technologies use local machine learning models to predict the results of intensive SPICE simulations from a few initial full-fidelity runs. However, it doesn’t just guess blindly. It constantly checks its own predictions against a confidence threshold, providing SPICE-accurate results. If a prediction falls outside this safe margin, the system automatically reverts to running a full-fidelity SPICE simulation to ensure correctness. This clever hybrid approach perfectly demonstrates the industrial-grade principles:

- It is accurate because it guarantees all results fall within the user-specified threshold.

- It is verifiable because it self-checks every single prediction for accuracy.

- It is robust because this trusted method can be reliably reused across different simulation conditions.

Another example is the recently launched Aprisa AI solution. AI design explorer, a major technology in Aprisa AI, uses machine learning and reinforcement learning algorithms to assist at all major stages of digital implementation and optimize workflows for optimal PPA results. Aprisa AI explores different flows within a targeted design space at each stage, taking into consideration the type of design and the designer’s chosen metrics. Aprisa AI makes decisions automatically on which paths to continue forward to the next stages of exploration, until it arrives to a full flow, and does so utilizing compute core resources more efficiently. While the agent can be launched and automatically make all the decisions to arrive at the best flow solution, Aprisa AI provides verifiability and flexibility to the designers. All databases at each stage are saved for user inspection and interaction with the data and logs. Aprisa AI design explorer also provides a dashboard with all the results of the explorations, allowing the designer to view all the metrics and examine why one approach might have a better PPA than another. Again, as in the above example, the principles of verifiability, robustness, ease of use, and generalizability remain true.

Leading the AI transformation of chip design

This journey for EDA AI is about more than just adopting consumer-grade AI; it is about adopting solutions that are accurate, robust, verifiable, usable, and generalizable. At Siemens EDA, we are committed to driving this transformation into chip design by developing solutions that engineers, managers, and executives can rely on for their most critical semiconductor designs. We believe the future of chip design won’t be built on generic chatbots, but by trusted, explainable, and industrial-grade AI partners fully integrated into every step of the semiconductor workflow. You can learn more about Siemens’ AI efforts here: EDA AI System | Siemens Software

About the author

Niranjan Sitapure, PhD, is the Central AI Product Manager at Siemens EDA. He oversees road mapping, development, strategic AI initiatives, and product marketing for the Siemens EDA AI portfolio. With a PhD in Engineering from Texas A&M University, Niranjan has honed his expertise in advanced AI/ML technologies, including time-series transformers, LLMs, and digital twins for engineering application. He can be reached at Niranjan.sitapure@siemens.com or on LinkedIn.

Also Read:

Hierarchically defining bump and pin regions overcomes 3D IC complexity

CDC Verification for Safety-Critical Designs – What You Need to Know

A Compelling Differentiator in OEM Product Design

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.