This webinar looks at the challenges a Design Engineer could face, such as when various IP blocks within an SoC are required to work in different clock domains to satisfy the power constraints.

Abstract:

Various IP blocks within an SoC are often required to work in different clock domains in order to satisfy the power constraints. Clock domain crossing (CDC) challenges faced by design engineers include:

– Speed and power requirements lead to designs with multiple asynchronous clock domains on different I/O interfaces and data being transferred from one clock domain to another.

– Transferring signals between asynchronous clock domains may lead to setup or hold timing violations of the flip-flops in the receiving clock domain.

– These violations may cause CDC signals to be metastable.

– Metastability may also arise from jitter between asynchronous clock domains, resulting in functional failures if the appropriate clock synchronizers are not present.

This webinar will examine the techniques used to avoid metastability as signals cross from one clock domain to another:

– Mux Synchronizer

– Two-Flip-Flop Synchronizer

– Handshake Synchronization

– Write operation

– Read operation

– Pulse

– Reset Domain Crossing

– Custom Synchronizer

Speaker Bio:

Freddy Nunez, a Senior Application Engineer at Agnisys since 2021, holds a degree in Computer Engineering from California State University, Northridge. He’s been instrumental in Agnisys’ success, leveraging his technical expertise to assist customers in navigating complex challenges and optimizing their systems. Freddy has experience with SystemRDL, IP-XACT, Verilog and SystemVerilog.

REGISTER HERE

Background:

The Agnisys IDesignSpecTM (IDS) Suite supports clock domain crossings (CDCs) from both the software (SW) and hardware (HW) sides. Techniques used to avoid metastability as signals cross from one clock domain to another include:

-

- Two-Flip-Flop Synchronizer

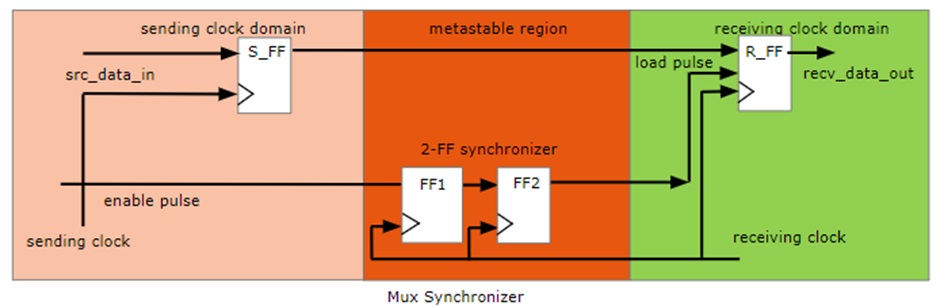

- Mux Synchronizer

- Handshake Synchronization

- Write

- Read

- Pulse

- Custom Synchronizer

In a CDC design, one clock is either asynchronous to, or has a variable phase relation with respect to, another clock. Speed and power requirements lead to designs with multiple asynchronous clock domains employed at different I/O interfaces and data being transferred from one clock domain to another. Transferring signals between asynchronous clock domains may lead to setup or hold timing violations of the flip-flops in the receiving clock domain. These violations may cause CDC signals to be metastable. “Metastability” refers to a state of indecision where the flip-flop’s output has not yet settled to the final expected value.

A typical register RTL block can be accessed either by a register bus on the SW interface and by application logic on the HW Interface.

Various techniques are used to avoid meta-stability as signals cross from one clock domain to another.

IDS supports multiple CDC synchronization techniques to synchronize data and control signals on the register block HW interface between the register block clock domain and the HW clock domain. These include simple 2-FF synchronization techniques with or without handshake, Mux Synchronizer and HW Write Pulse Synchronizer.

IDS also supports a custom synchronizer flow where the “2-FF wr_req Synchronizer” and “2-FF wr_ack Synchronizer” will be replaced with back2back sync flop modules giving users the flexibility to add custom implementations for their FF chain.

IDS also supports SW Interface CDC when it is required that the Register RTL block operates on a clock different from the Register bus clock. In this case, transactions coming from the bus will first get translated into a custom bus and then custom control and data signals are synchronized into the Register block bus domain using appropriate Handshake synchronization techniques.

REGISTER HERE

Also Read:

An Update on IP-XACT standard 2022

WEBINAR: Driving Golden Specification-Based IP/SoC Development

The Inconvenient Truth of Clock Domain Crossings

Share this post via:

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era