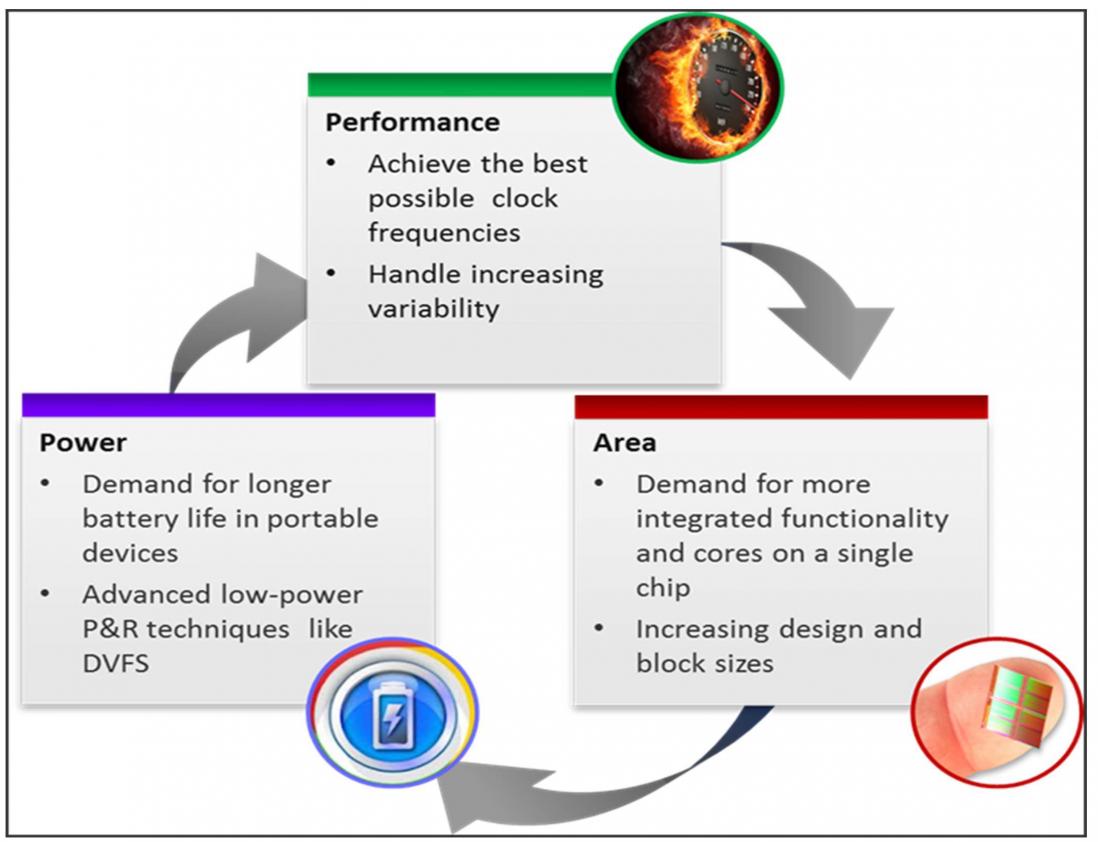

How do you ensure your design has been optimized for power, performance, and area? I posed this question to Mentor’s Group Director of Marketing, Sudhakar Jilla and product specialist Mark Le. They said that finding the PPA sweet spot is still often done by trial and error – basically serial experiments with various input parameters until the target specs are met.

How do you ensure your design has been optimized for power, performance, and area? I posed this question to Mentor’s Group Director of Marketing, Sudhakar Jilla and product specialist Mark Le. They said that finding the PPA sweet spot is still often done by trial and error – basically serial experiments with various input parameters until the target specs are met.

Is this efficient? Clearly not. It could take weeks or months or really never come to fruition because of deadlines. Jilla and Le say that the ugly reality of finding the optimal PPA under the pressure of tight design schedules has been ripe for better EDA solutions.

What’s needed is an RTL-level automated “design space exploration” that lets designers simultaneously explore various design alternatives prior to implementation. The solution must be efficient, easy to use and provide the most useful analysis in the shortest time.

Mentor offers a design space exploration solution in their physical RTL synthesis tool, Oasys-RTL. Jilla says it is different than other available ‘what-if’ analysis solutions because it works at a higher level of abstraction, which makes it faster, while still achieving a good level of accuracy. He said it is also pretty easy to use. Oasys-RTL’s integrated commands control the various configurations; the designer just modifies existing synthesis scripts to add new variables to define the functionality of the desired exploration.

Download the new whitepaper RTL Design Space Exploration for Best PPA Using Oasys-RTL.

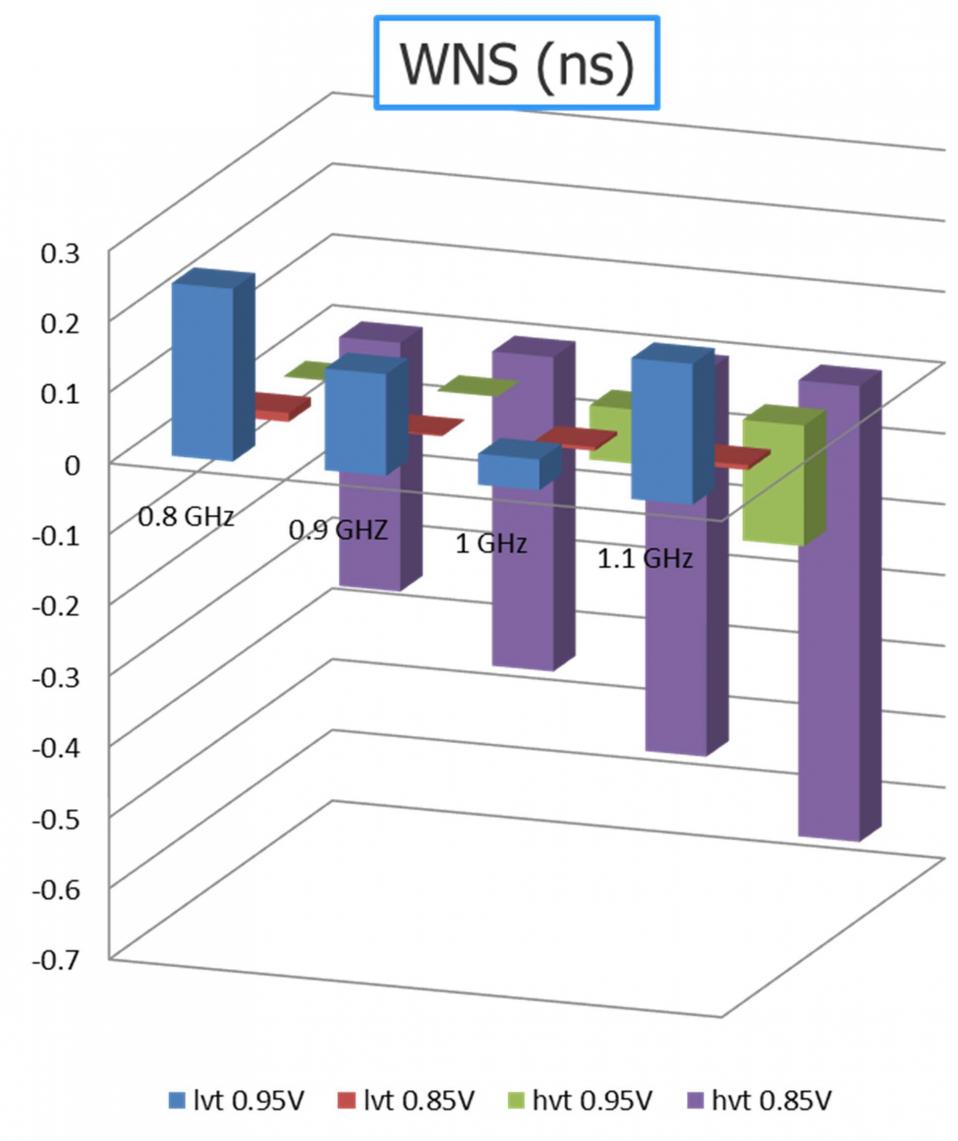

For example, Le poses a situation in which a designer needs to determine the top frequency at which the design can meet timing. If the performance is set too high, critical timing paths will be extremely difficult to close. Also, large SOCs have multiple complex clocks and frequency tuning becomes a challenge when there are tens or hundreds of clocks. Say the design uses four multi-vt libraries with four target frequencies.

Library: LVT 0.95 V, LVT 0.85 V, HVT 0.95 V, HVT 0.85 V

Frequency: 0.8 GHz, 0.9GHz, 1.0 GHz, 1.1 GHz

There are 16 different combinations, or scenarios, to analyze. Oasys-RTL processes each of the 16 scenarios as if they were individual configurations, and then provides a comprehensive summary of results for comparison. The results show the design meets the 0.9 GHz timing target for both LVT libraries.

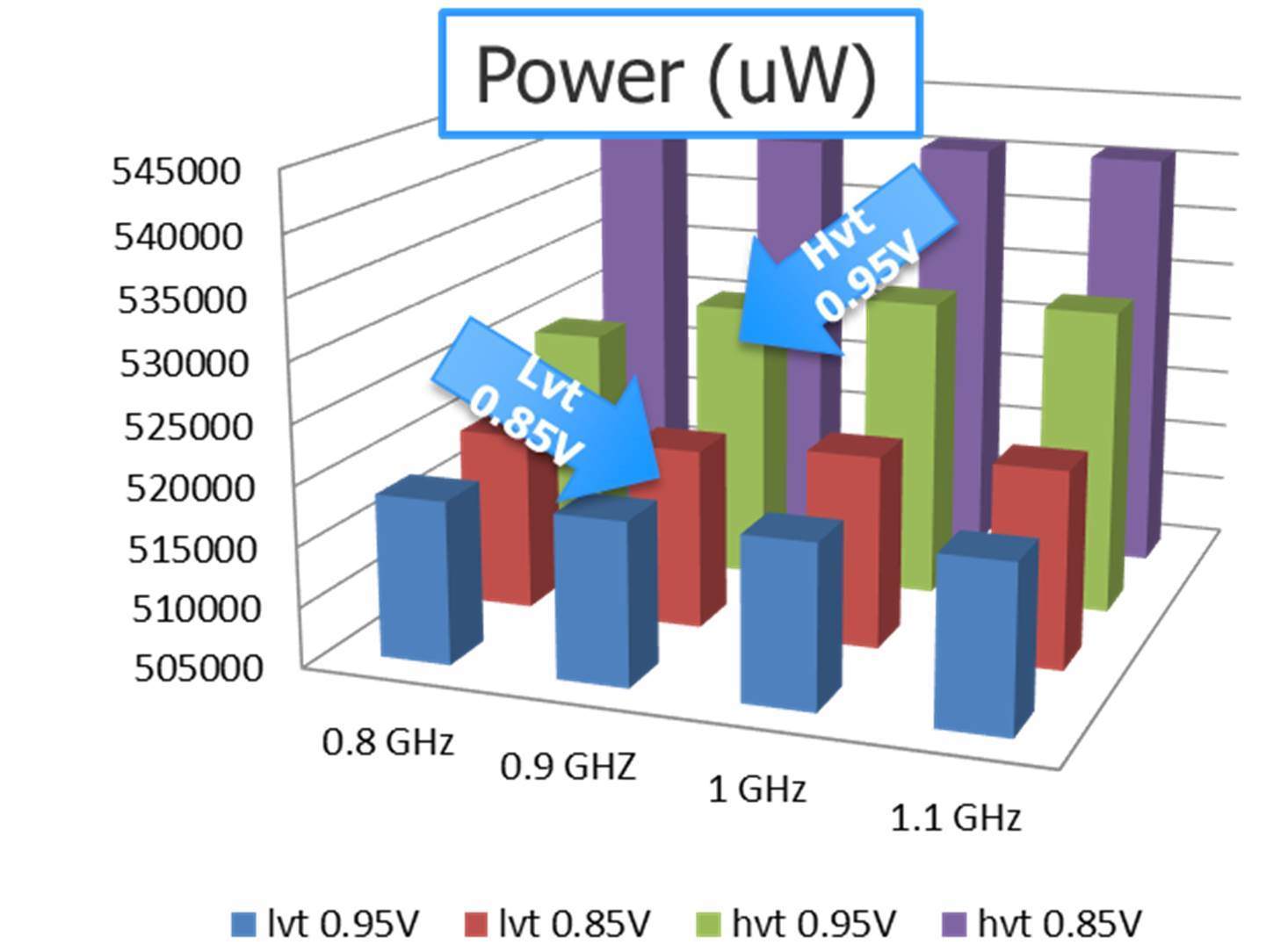

Say you also want to include power in this analysis. Le points out to a case in which the results were counter-intuitive because the HVT 0.95 V library consumed more power than the LVT 0.85 V library. It turns out that the slower HVT library requires more optimization to meet timing, which causes increased area and power.

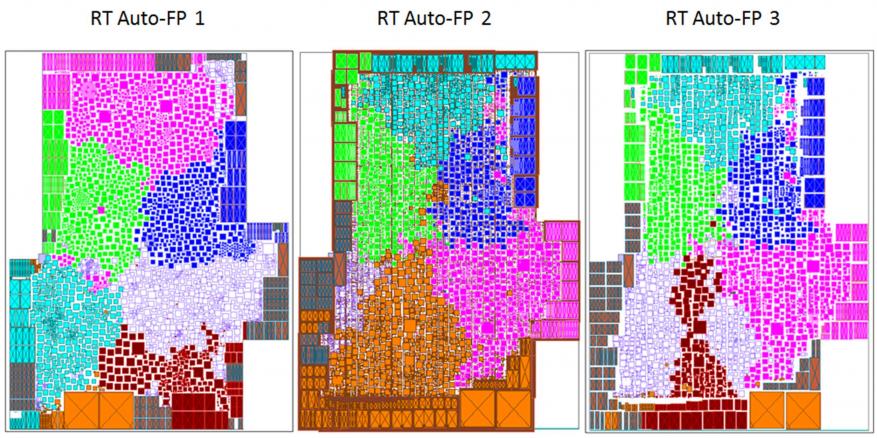

What about floorplan exploration? Jilla says that Oasys-RTL reads in the entire design and automatically creates a floorplan based on the high-level RTL modules and design data flow. Because it uses a patented “PlaceFirst” technology, physical placement information is available early in the design flow for accurate timing and congestion analysis.

Starting from scratch, you can set utilization targets for the design and use a design space exploration command to scale the values automatically, stepping through higher or lower increments. Other physical attributes can be manipulated as well to change aspect ratios, die size, macro grouping, macro packing, pin locations, etc.

This image shows three unique production-quality floorplans in parallel based on different recipes. Jilla says that real customer experiences have shown that Oasys-RTL reduces the time required to generate production quality floorplan to a matter of days.

This image shows three unique production-quality floorplans in parallel based on different recipes. Jilla says that real customer experiences have shown that Oasys-RTL reduces the time required to generate production quality floorplan to a matter of days.

The analyses generate reports that can be saved to a comma separated values (.csv) file to import into a spreadsheet. The CSV format can further be employed to create graphs, charts and scatter plots to help visually analyze the metrics. From this vantage point, managers can decidedly select the best power, performance, or area.

To learn more about the getting the best PPA with Oasys-RTL’s design space exploration, download the new whitepaper from Mentor.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.