Introduction

3D field solvers produce the most accurate netlists of RC values of your IC layout that can then be used in SPICE circuit simulators however most of these solvers produce a flat netlist which tends to simulate rather slowly. Thankfully several years ago the first hierarchical SPICE tools were offered by Nassda (HSIM) and Cadence (UltraSim) but they require a hierarchical netlist to simulate large designs quickly and efficiently.

3D field solvers produce the most accurate netlists of RC values of your IC layout that can then be used in SPICE circuit simulators however most of these solvers produce a flat netlist which tends to simulate rather slowly. Thankfully several years ago the first hierarchical SPICE tools were offered by Nassda (HSIM) and Cadence (UltraSim) but they require a hierarchical netlist to simulate large designs quickly and efficiently.

What’s New?

This week I spoke with Dermott Lynch of Silicon Frontline about their latest Hierarchical 3D Field Solver named H3D.

Q: What is hierarchical extraction a big deal?

A: Most SOCs have many memory and other repeated structures in their layout, so exploiting layout hierarchy provides a big benefit to users.

Q: What kind of approach did you use with H3D to create a hierarchical netlist?

A: We have a patented approach based on the Random Walk Algorithm, interested readers can see the patent here.

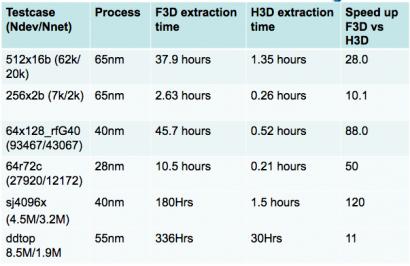

Q: How are the CPU run times with your hierarchical approach to extraction?

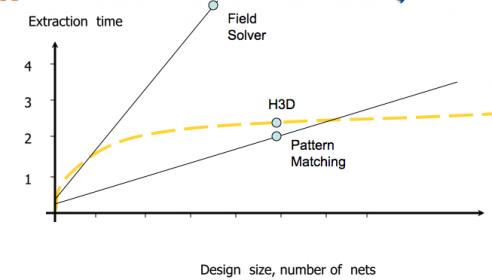

A: This new tool shows a sub-linear increase based on the number of nets.

Q: Does H3D fit into my existing IC tool flow?

A: Yes, it reads a standard layout and produces a netlist that can be: distributed, lumped, C, R, RC and RCCc.

Q: How about using distributed CPUs?

A: We support both distributed and multi-core CPUs to help speed up the results.

Q: Compared to a flat extractor, what kind of speed improvements should I expect with this hierarchical extractor?

A: From 10X to 100X speed improvements, based upon how much hierarchy there is in your layout. Designs with the most hierarchy are: FPGA, Image Sensors and memory rich SOCs.

Q: Should I expect the RC numbers extracted from your flat tool to match the hierarchical tool?

A: Yes, they are statistically equivalent values.

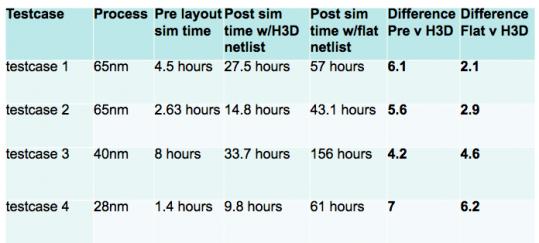

Q: How does H3D help my post-layout simulation run times?

A: We’re seeing speed improvements between 2X and 7X faster using the H3D netlist in a Fast SPICE simulator.

Q: How popular are your field solver tools?

A: Over 350 designs have been verified at over 30 customers, and they’ve been adopted by 12 of the top 30 semiconductor vendors.

Q: What is pricing like for H3D?

A: Pricing starts at $99K annually and there are several configurations to choose from.

Summary

If your IC design requires the highest accuracy for parasitic RC values and the layout has hierarchy then you should start to consider the tool flow of H3D for hierarchical extraction followed by a Fast SPICE tool like HSIM or UltraSim.

*Note: to read/write comments you must log in.

Share this post via:

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era