Portable Stimulus has become such a popular standards topic of late that I thought it would be good to take a break this month from my low power series to bring you, my valued readers, more information about it from one of my colleagues, Dennis Brophy, who is working to help drive development of this standard within Accellera. I’ll be back in December to continue my low power series.

Ellie, thank you for the opportunity to share details on the standardization of Portable Stimulus — an emerging standard that is set to offer a quantum boost in verification efficiency and expand the reach of vertical reuse in the design process. I along with many others in the industry are engaged in the Accellera Portable Stimulus Working Group to make sure this happens in a way that is most beneficial to all of our customers.

First I should share a little history about how this came about and why we wanted to collaborate with others to drive development of this standard. Around DVCon 2014, Mentor Graphics approached Accellera with a proposal for a new standard building upon some unique verification technology. We wanted this technology to benefit from the next level of openness, standardization, and, most importantly, interoperability to promote expanded use by the design and verification community. To start the process, Accellera initiated a Proposed Standards Working Groupthat allowed everyone who wished to participate to come together to determine if it made sense to form a formal working group, which would create the standard.

At Mentor Graphics we were prepared to commit our technology to seed the standard’s development as we have seen customers gain a ten-fold increase in coverage closure by using it to exhaustively cover a device’s state space more rapidly. So we knew this would be highly beneficial. However, in real-world design verification, users often need to share their verification descriptions with others whom they may have business relationships. After all, most modern SoCs are comprised of blocks from numerous sources or companies that are not all guaranteed to be users of our technology. This posed an interoperability problem that a standard could help address.

The Accellera team recognized that the ability to express specific intent and behaviors should also be reusable across different target platforms; such as emulation, simulation, FPGA prototyping, post-silicon, and more. It was also not lost on Accellera, or those practicing functional verification today, that several different languages and techniques are used to generate verification stimulus, depending on whether one is working at the block-level, subsystem, SoC, or the system-level. It is also well understood that embedded software plays a key role to drive stimulus in SoC and system-level environments; yet current languages offer little, if anything, to adequately support this.

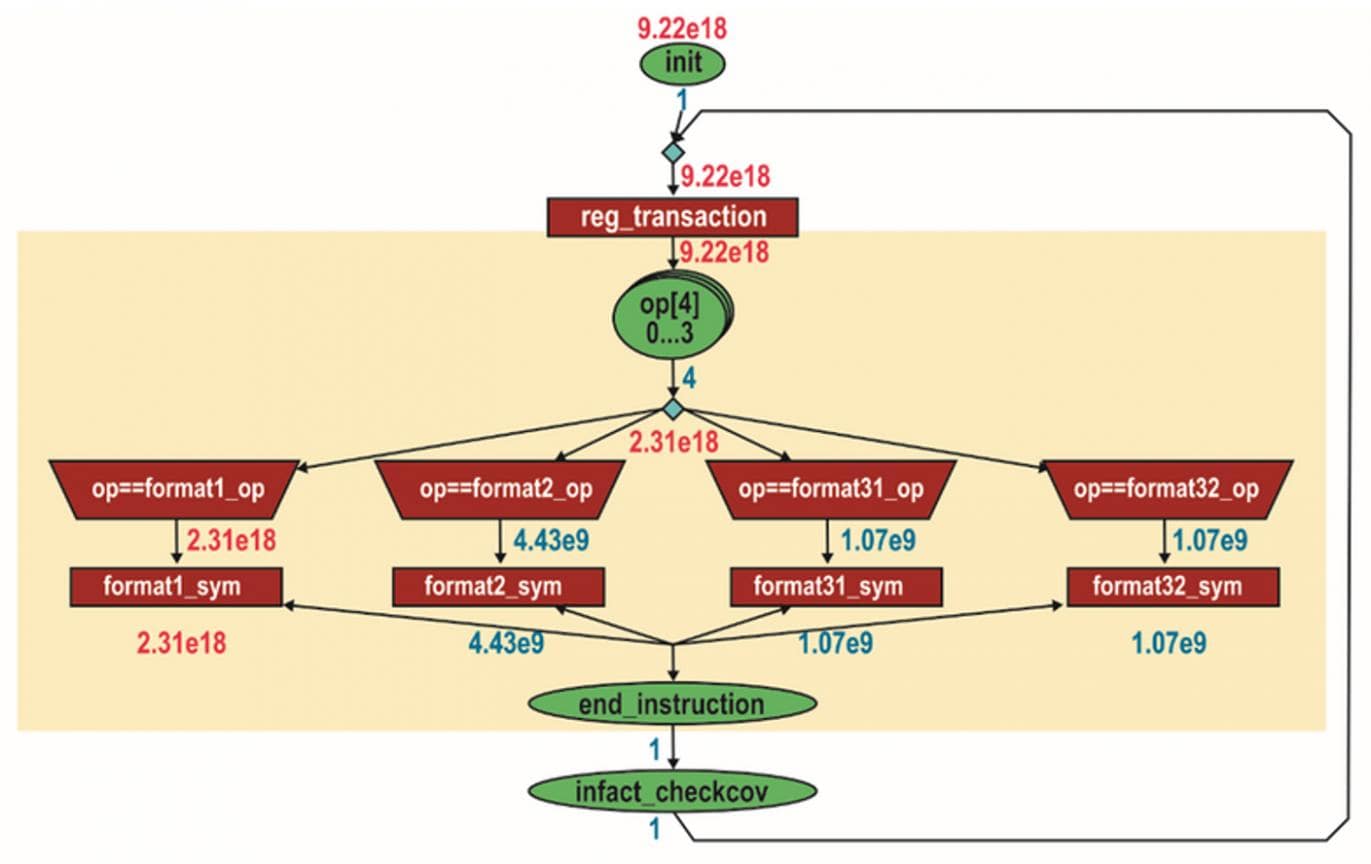

The Portable Stimulus Working Group (PSWG) was approved as an official working group at the end of 2014 and has been in full operation all of 2015. First, the group gathered requirements and called for contributions. In response, several companies offered technology that fulfilled many of the requirements. In this process, one fundamental technology Mentor Graphics contributed was our graph-based test specification, as offered in our inFact™ solution. Even better than a contribution from us alone, Cadence Design Systems and Breker also contributed, setting the stage for a standard that can be practiced by several suppliers for the benefit of all consumers.

The involvement of multiple solution suppliers and the success of solutions already in the market that are advancing design verification efficiency are two big reasons Portable Stimulus presentations have led to packed conference events – such as the last two DVCon India conferences. At DVCon India 2014, Portable Stimulus was the talk of the event. And at DVCon India 2015, the early-morning, birds-of-a-feather, pre-conference meeting saw a full room – and a commitment by those attending to brave the traffic and extra-early morning departures to reach the venue.

As many share my opinion that graph-based verification methods will usher in the next level of verification efficiency and that Accellera’s Portable Stimulus standard will help this happen, some may wonder what the basis for this opinion is. As mentioned earlier, at Mentor Graphics we have direct proof of this efficiency from our practice today. And the industry knows that a graph-based specification format is not new to verification. It is based on the standard Backus-Naur Form (BNF), pioneered by IBM, and has been used by many companies to automate compiler testing.

The task at hand now is to ensure that the use of the Portable Stimulus notation emerging from Accellera can address the group’s requirements such that it will improve vertical reuse and support the design verification environments, methodologies, and languages in use today. Accellera working groups are membership-based development activities. You will find some public information at the Accellera Portable Stimulus Working Group website, but the vast majority of detailed technical information and deliberation on contributions requires membership.

Given the fast pace of requirements gathering and review of technology contributions, my guess is there will be more public information for non-members in 2016, so they can also learn more about this important emerging standard.

In advance of public information from Accellera, we already have lots of material for you at mentor.com and the Verification Academy.

A couple of good resources are a paper on how a portable stimulus specification can be applied to make instruction-stream generation simpler, A New Stimulus Model for CPU Instruction Sets,on the Mentor Graphics Functional Verification web site.

And the video, New School Stimulus Generation Techniques, puts a spotlight on Mentor’s Questa inFact graph-based portable stimulus tool.

Share this post via:

Comments

0 Replies to “Coming to a Workstation Near You: Accellera’s Portable Stimulus Standard”

You must register or log in to view/post comments.