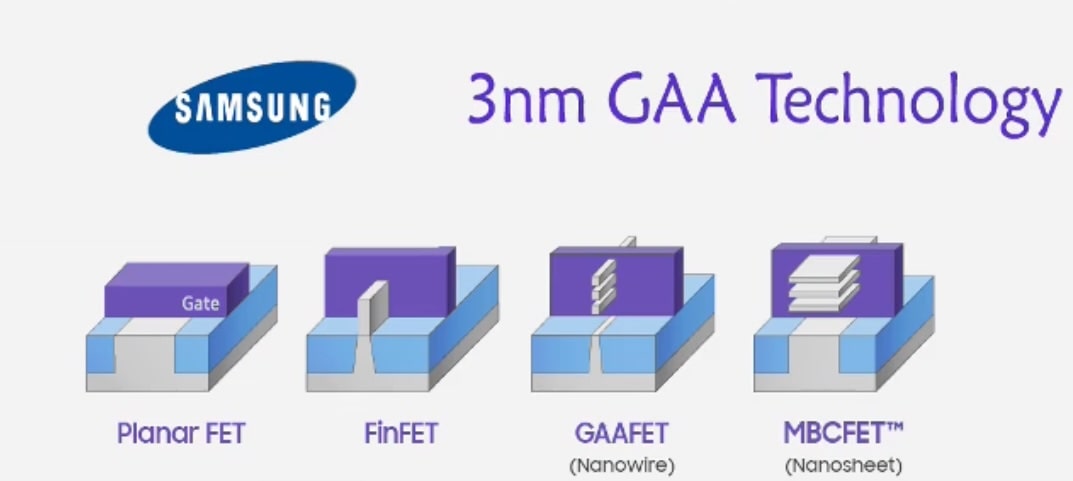

Transistor fabrication has spanned the gamut from planar devices o FinFET to Gate-All-Around (GAA) as silicon dimensions have decreased in the quest for higher density, faster speeds and lower power. Process development engineers use powerful simulation tools to predict and even optimize transistor performance for GAA devices. Dr. Philippe Blaise, Principle AE at Silvaco delivered a webinar on the topic of simulating GAA devices using their tool, Victory Atomistic with quantum-level precision.

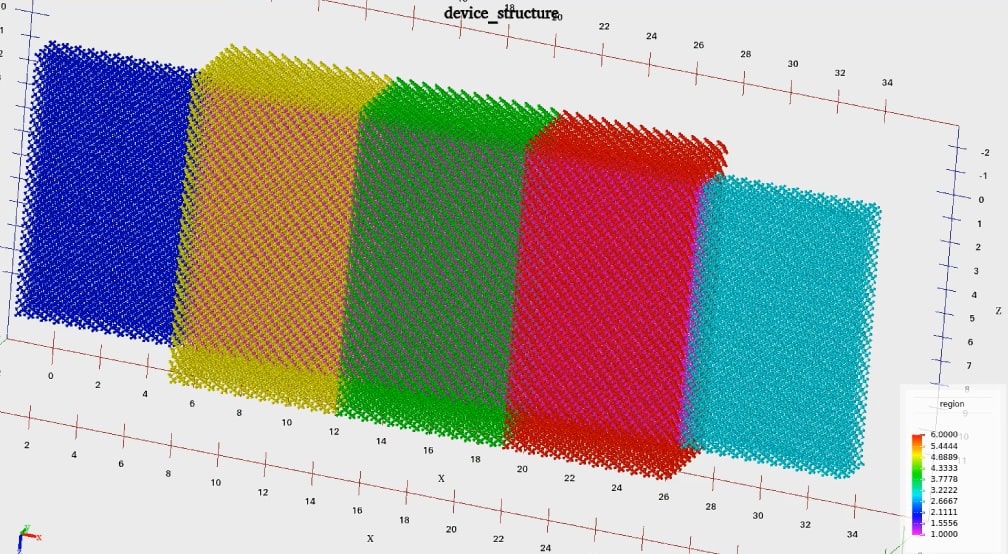

An overview diagram shows the different FET device structures in 3D cross-sections.

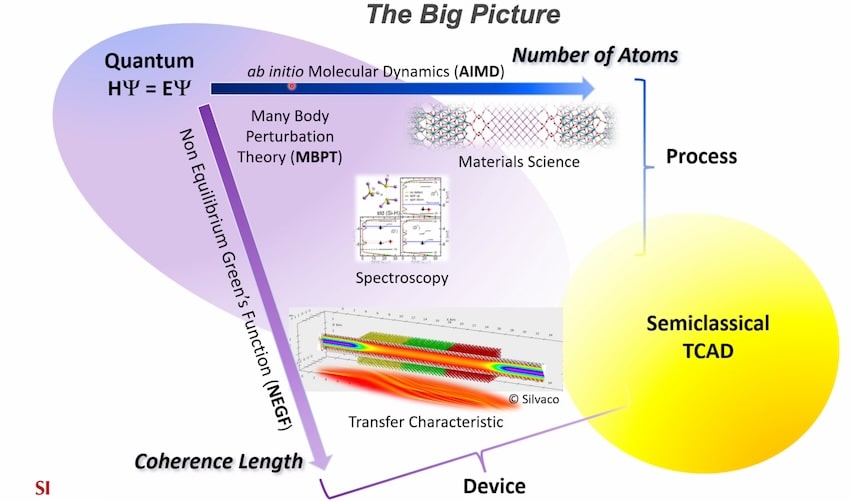

The big challenge is how to simulate a GAA FET and predict its performance at the nano scale with quantum effects, easy for a TCAD engineer to use, fast enough to enable exploration and optimization, and accurate enough to produce trusted SPICE models. Silvaco uses the Non Equilibrium Green’s Function (NEGF) approach in their device simulation.

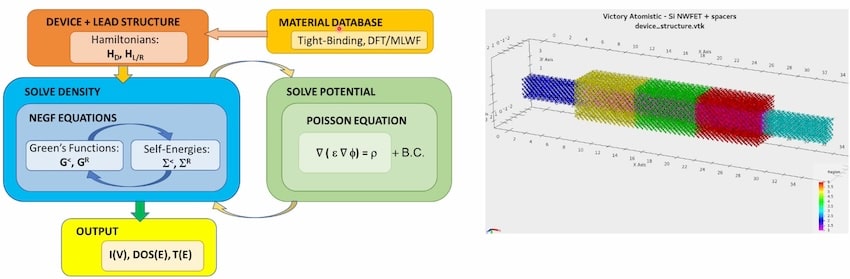

Using Victory Atomistic looked straight forward, where the user chooses a material from a database, defines the device structure, then the simulator solves density using NEGF equations and solves potential using Poisson’s equation, producing an output IV curve.

Dr. Blaise showed the details of the device template for a nanowire using a diamond crystal structure in Silicon, with lengths, number of gates, doping, oxide and contacts. Users also choose the type of solver, voltage ranges, temperature and output options. The goal of Victory Atomistic is to enable atomic-scale TCAD simulations easy to use by keeping the complexity inside the tool.

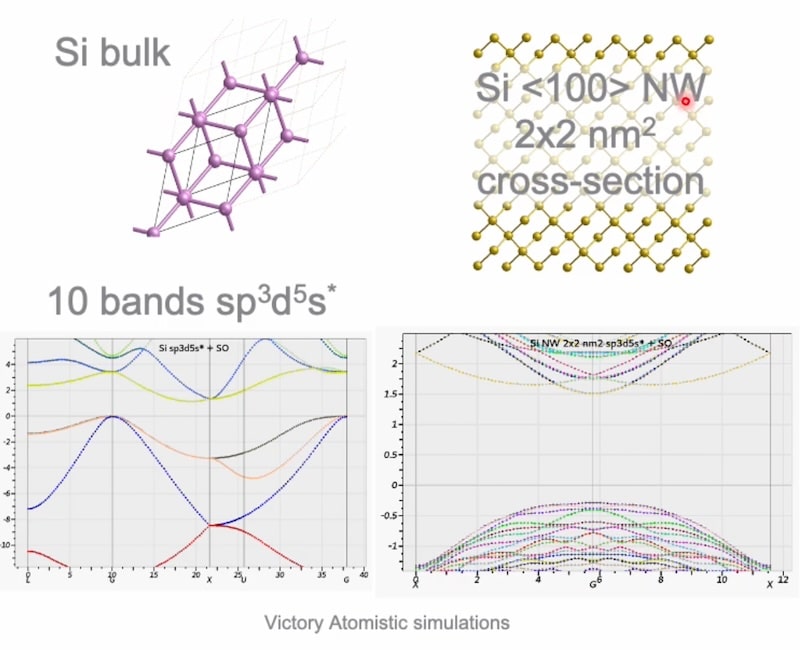

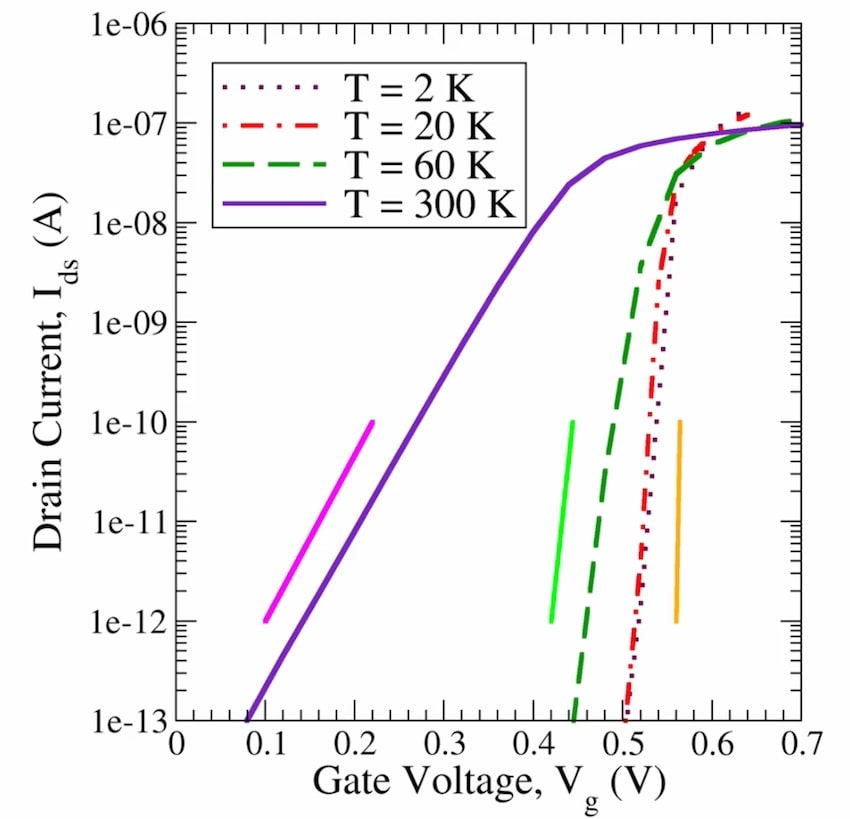

Simulation results showed the desired accuracy, along with options for silicon bands and orientation. Victory Atomistic uses the Low-Rank Approximation (LRA) optimization technique to make the complex, quantum-level simulations run in a short period of time on conventional computers.

SiGe materials were simulated using Virtual Crystal Approximation (VCA). Transition-metal dichalcogenide (TMD) monolayers were also simulated for MoS2. Electron-phonon scattering effects were modeled next. Victory Visual was demonstrated as a graphical post processing tool, showing 90,000 atoms loaded.

Simulation results for a GAA FET device showed accurate results across a temperature range of 300K to 2K.

Summary

GAA FET devices can be accurately modeled and simulated using the NEGF algorithm, so that TCAD engineers can predict and optimize a new process technology. Silvaco has made their Victory Atomistic tool easy to use, and the results are produced quickly with the option to employ multiple CPUs. Victory Visual helps to graphically show results, making analysis more intuitive. Simulating a process technology before running wafers saves time and money, so why not give modern TCAD tools a try.

View the entire webinar after registering online here.

Related Blogs

- Silvaco: Navigating Growth and Transitions in Semiconductor Design

- Analysis and Exploration of Parasitic Effects

- Accelerating IC Design: Silvaco’s Jivaro Parasitic Reduction Tool

- Silvaco’s Diffusion of Innovation: Ecosystem Investments Driving Semiconductor Advancements

- Silvaco at the 2025 Design Automation Conference #62DAC

- TCAD for 3D Silicon Simulation

![SILVACO 051525 Webinar 400x400 v2[62]](https://semiwiki.com/wp-content/uploads/2025/04/SILVACO_051525_Webinar_400x400_v262.jpg)

Comments

There are no comments yet.

You must register or log in to view/post comments.