Switched-capacitor circuits are used in most CMOS mixed-signal ICs as:

- Track and hold circuits

- Integrators

- Operational Amplifiers

- Delta-sigma modulators

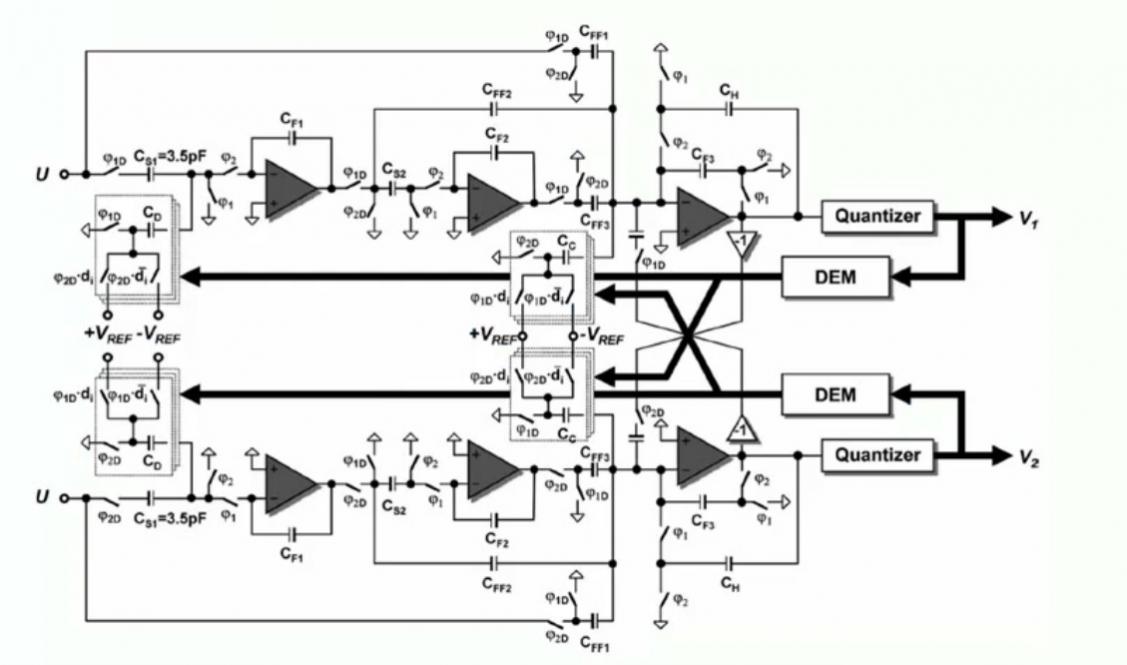

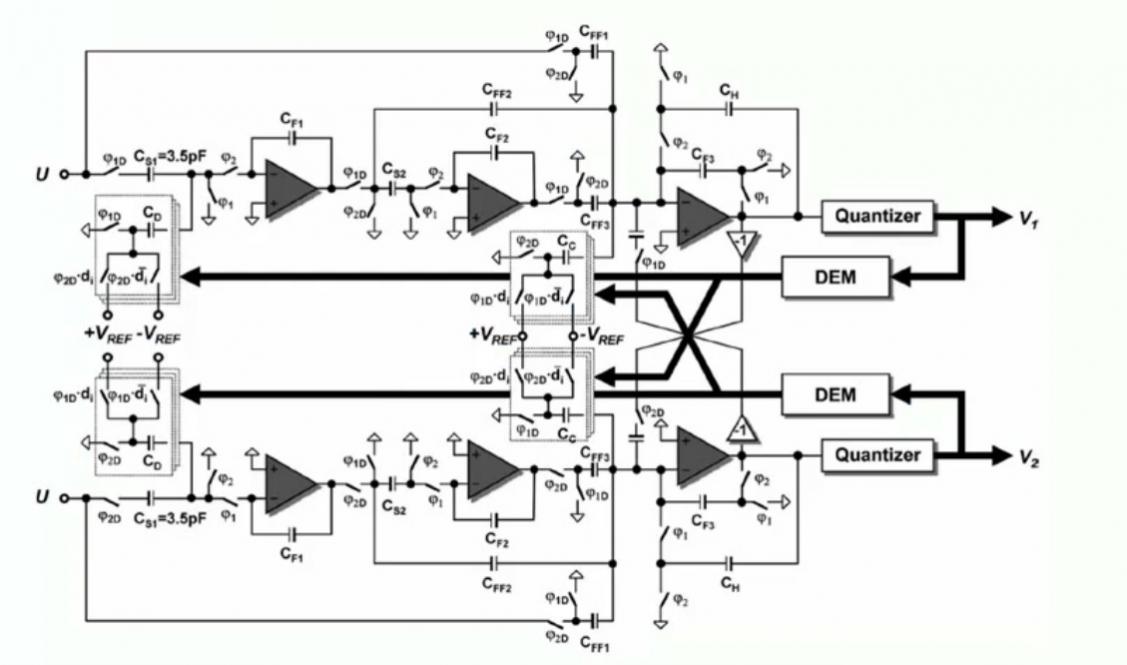

Delta-Sigma Modulator: IEEE J. Solid-State Circuits, vol. 43, no. 12, pp 2601-2612, Dec. 2008

SPICE circuit simulators are used during the design phase and measure the performance. One type of analysis is called device noise analysis and the thermal noise in MOS switches is the major performance limiter.

Berkeley Design Automation presented a webinar on this topic, and I’ve watched the archived version to blog about it.

Dr. Boris Murmann, Stanford University

Switched-Capacitor Noise Analysis Theory

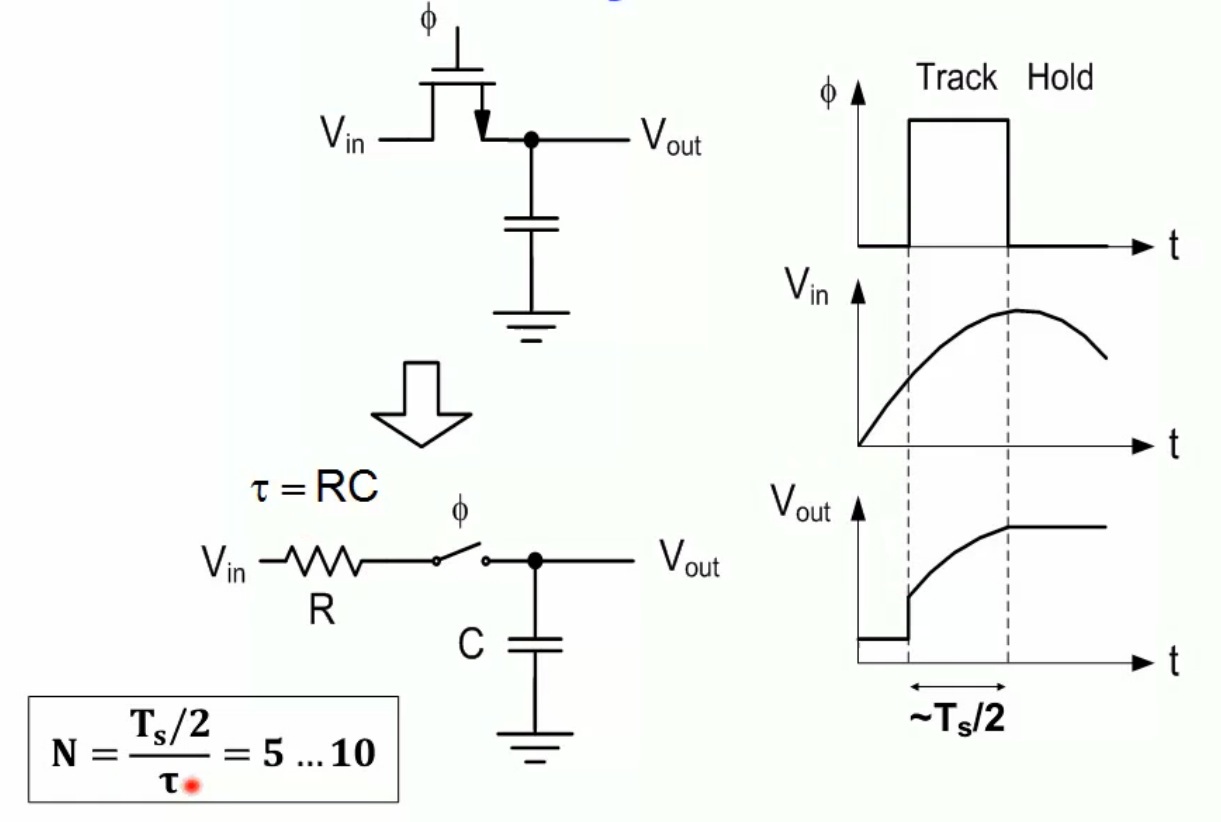

Starting with a track and hold model using a single MOS switch and capacitor, we clock the gate of the MOS device using a signal called Phi which transfers the voltage on Vin to the node called Vout during the Track time, then Holds the voltage on capacitor C.

The higher the number N, the more frequent you are sampling which improves accuracy.

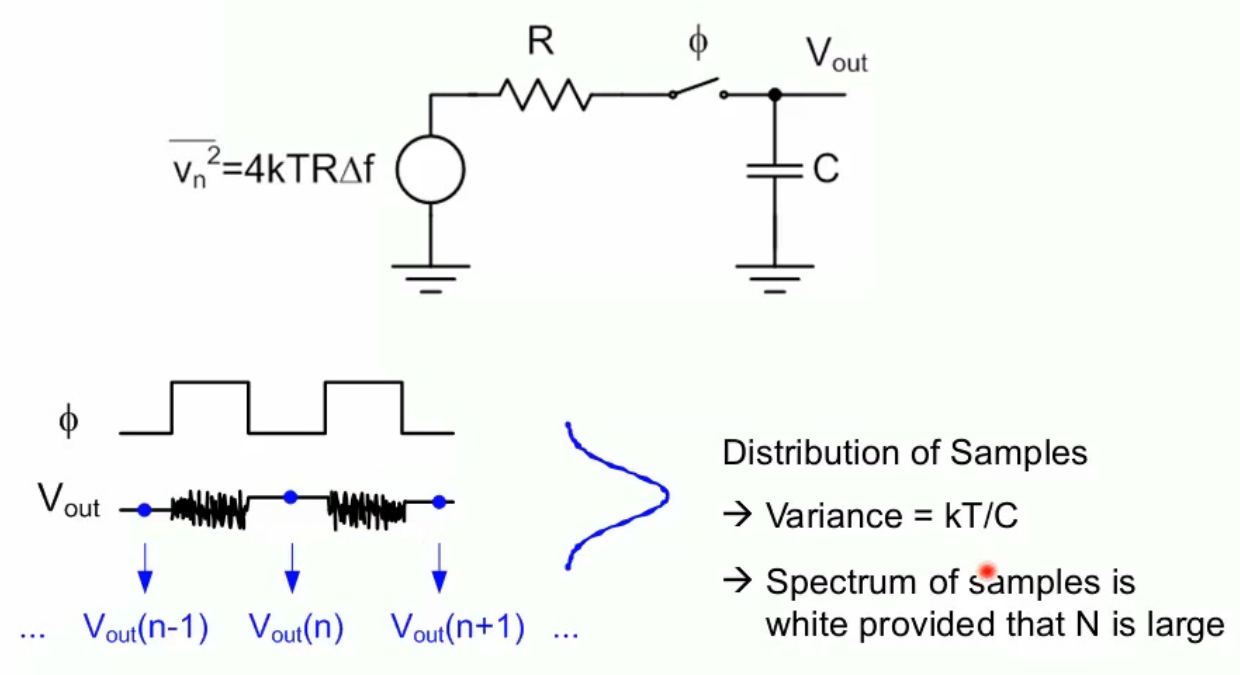

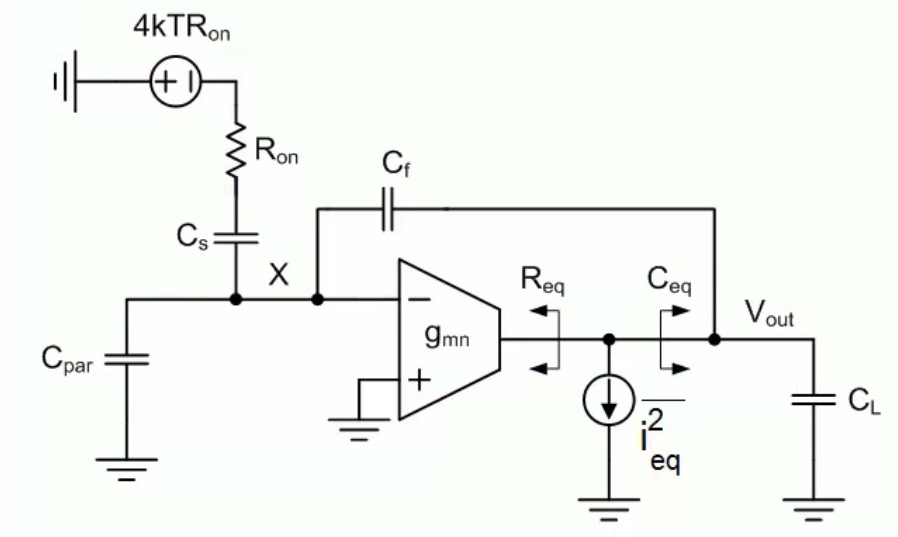

Noise analysis for a track and hold circuit can be calculated using an equivalent circuit.

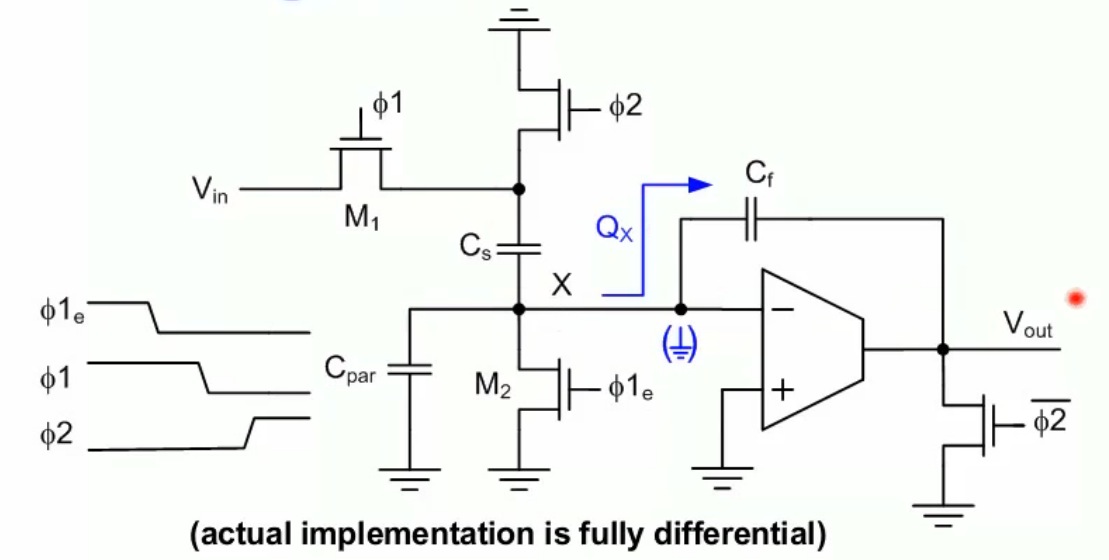

More complex circuits combine multiple track and hold circuits, and we can model the Phi1 behavior using charge conservation as Vout = (Cs/Cf)*Vin:

Noise analysis for this circuit simplifies with the Equipartition Theorem to be: kT( Cs + Cf + Cpar)

Notice that parasitic capacitance Cpar will worsen our noise number.

During Phi2 we take into account the behavior of the Op-Amp in our noise model:

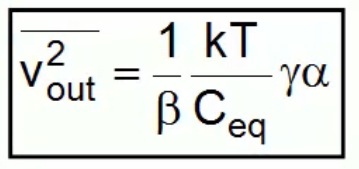

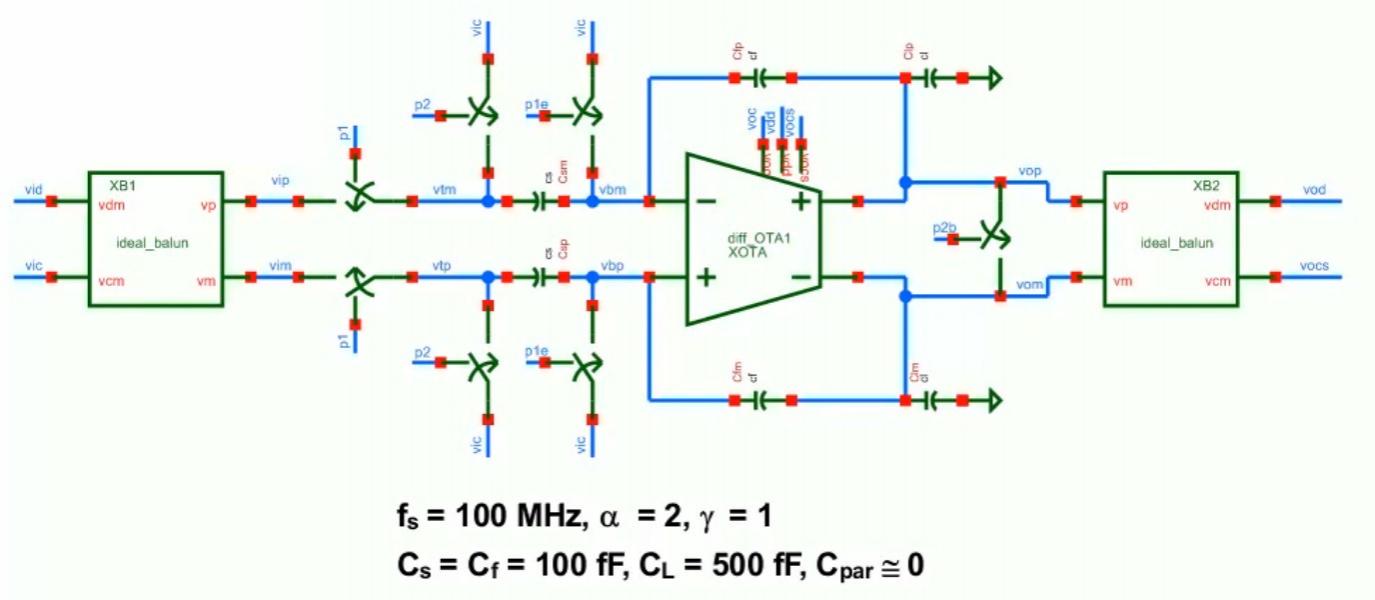

After simplifying assumptions the output referred noise is described as:

Adding up both Phi1 and Phi2 noises, we have equations for output and input:

Switch-Capacitor Noise Simulation

To verify that these noise equations are valid you could simulate in SPICE using .AC or .NOISE analysis. Another approach is to use Period Steady State Simulation (PSS). Finally, you could run a Transient Noise analysis by adding noisy sources.

BDA Simulation Results

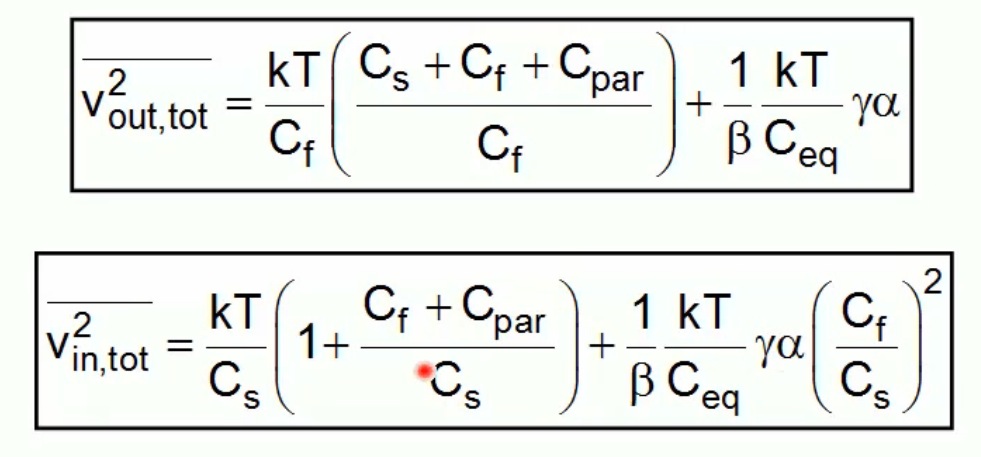

The following track and hold circuit was simulated using Berkeley’s Analog FastSPICE circuit simulator with PSS analysis:

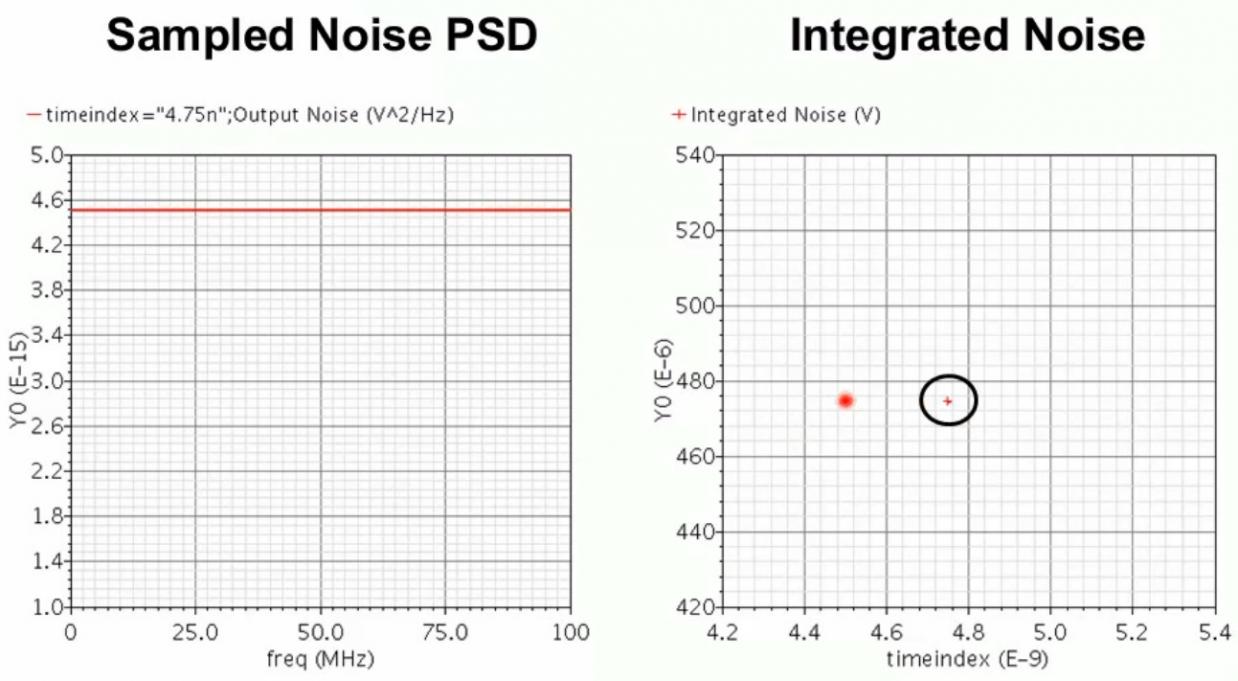

The simulator produces values for both sampled noise and integrated noise:

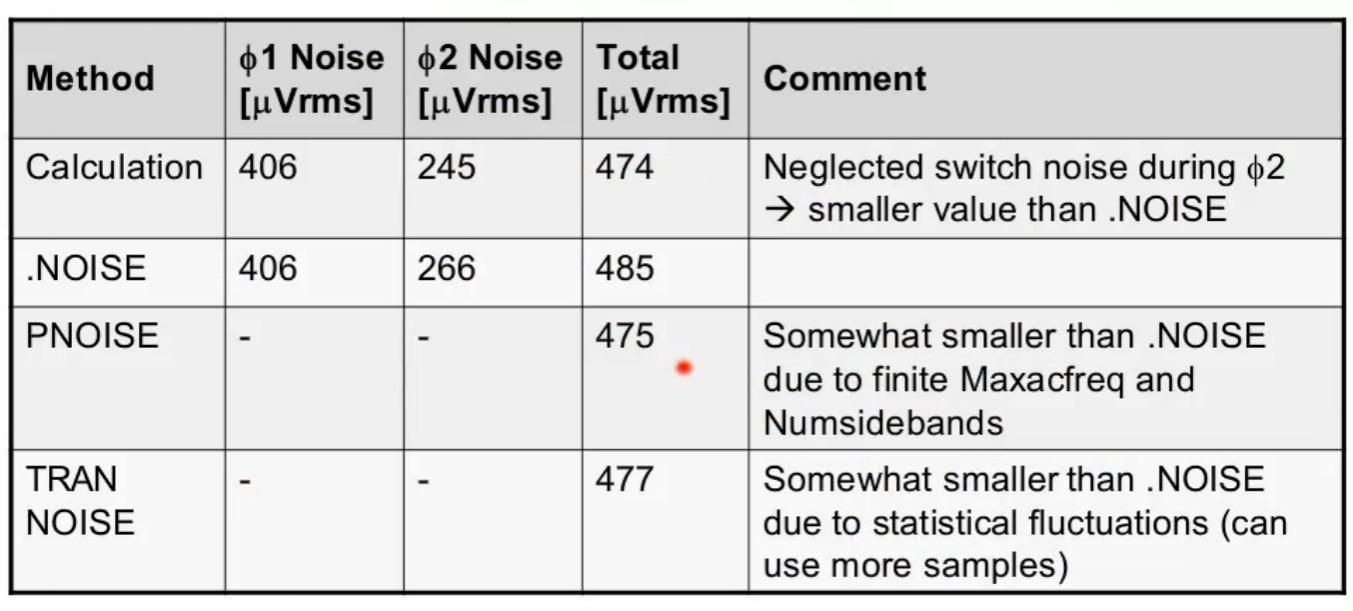

There’s good agreement between the theoretical hand calculations and simulated results for all three simulation approaches:

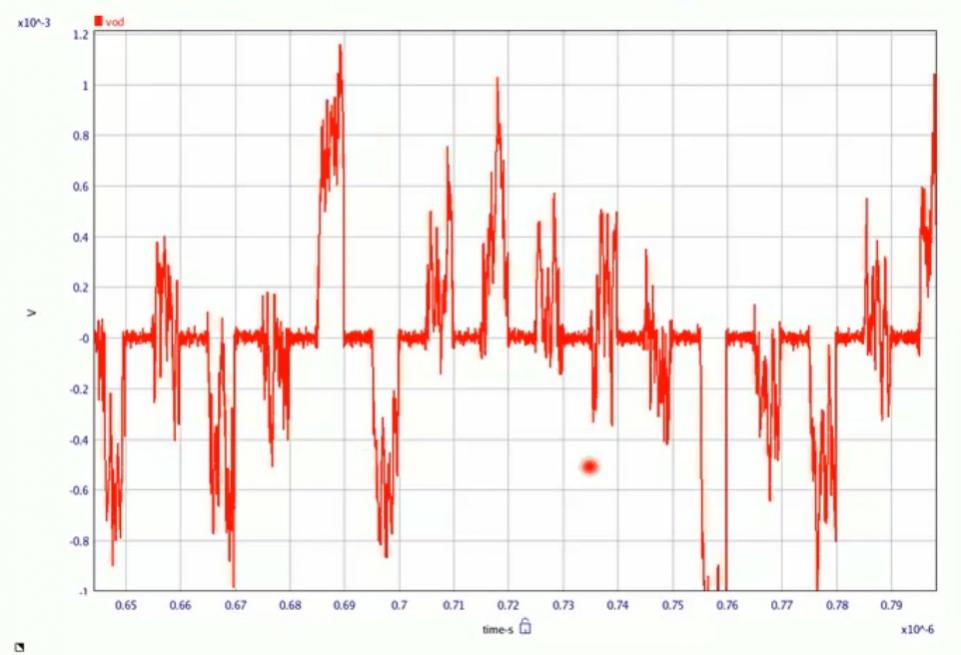

Transient Noise can also be simulated with the BDA tool for this switched-capacitor circuit, showing most of the noise happens during Phi2:

Some benefits of using Transient Noise analysis are:

- Larger capacity circuits can be simulated, compared to PSS and PNOISE

- Waveforms show you intuitively where the noise happens

- Can be used on non-periodic circuits as well

- No need to manually combine results from .AC and .NOISE analysis

David Lee, Berkeley DA

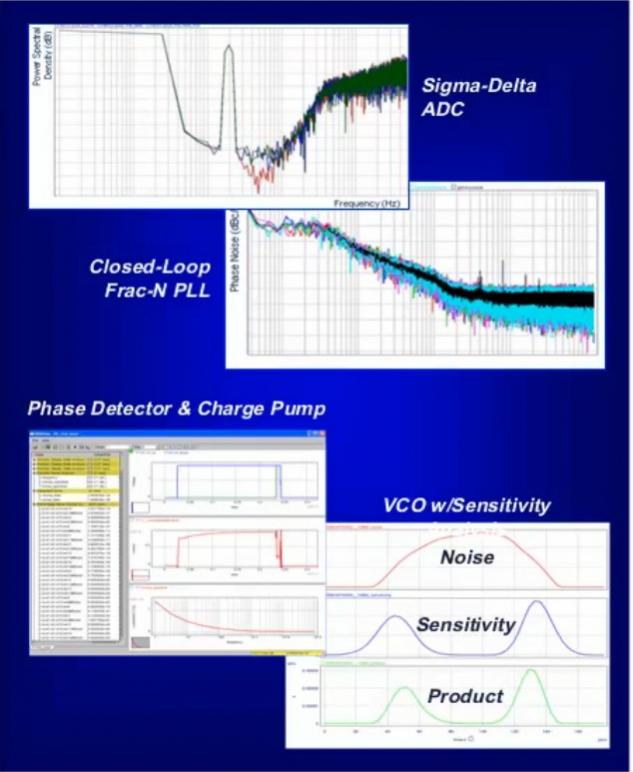

The Analog FastSPICE circuit simulator from Berkeley DA provides full-spectrum device noise analysis for:

- Transient Noise Analysis

- Periodic Noise Analysis

- Oscillator Noise Analysis

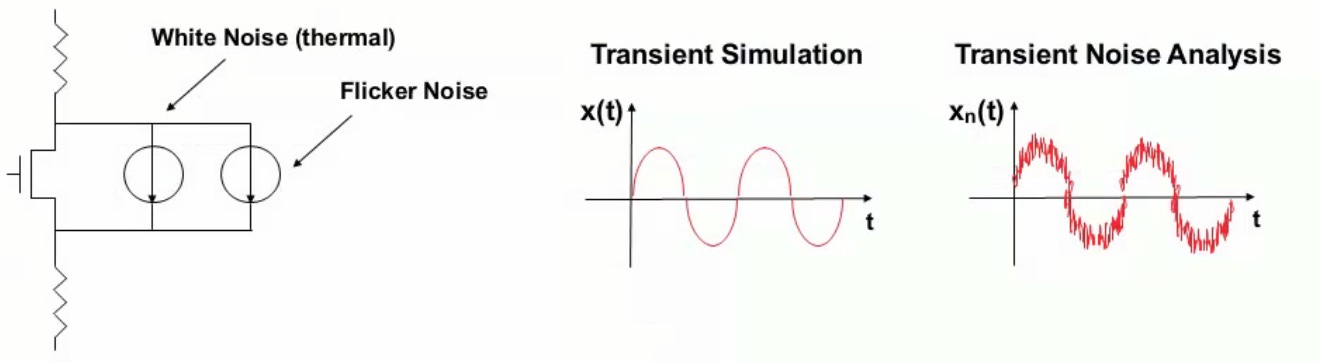

The Transient Noise Analysis in Berkeley’s simulator automatically adds noise sources to MOS devices, and solves stochastic differential equations for every node, every time step:

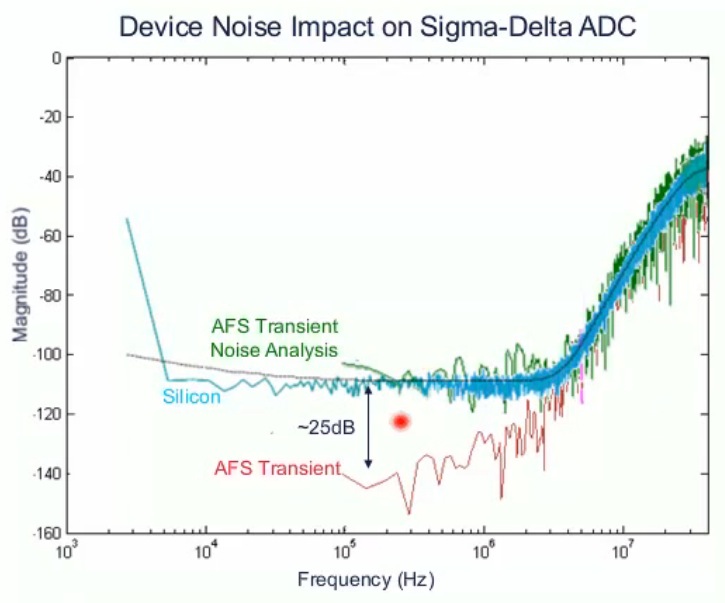

Qualcomm used Berkeley’s AFS tool and showed close correlation of Device Noise versus measured silicon results for a Sigma-Delta ADC:

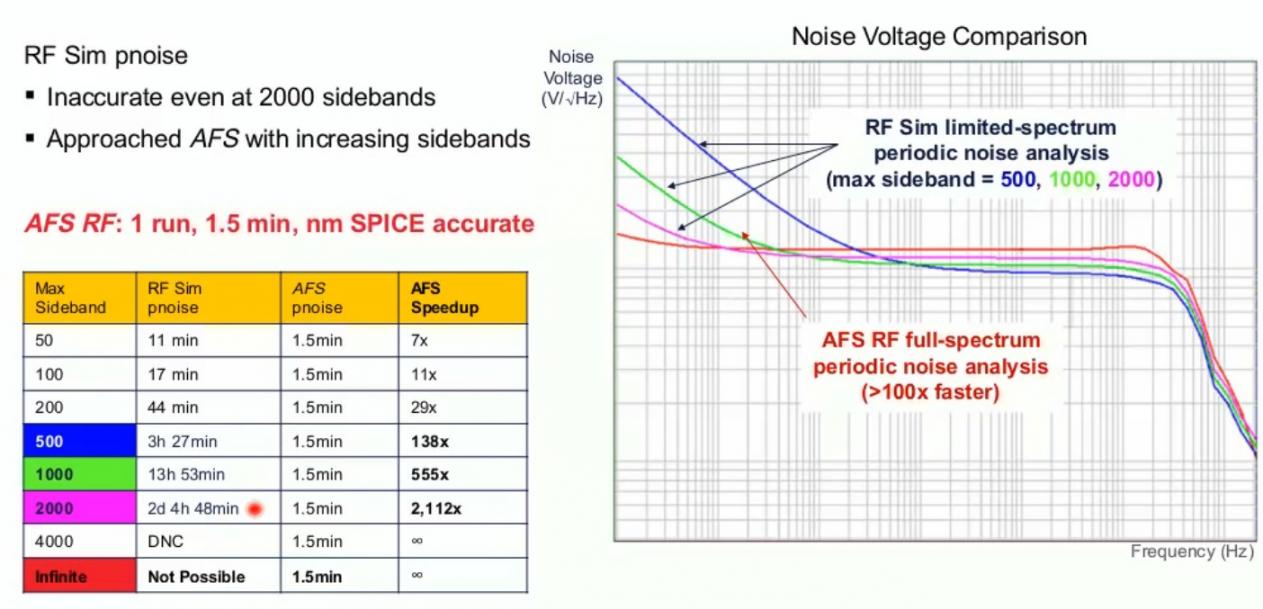

Another customer simulated PNOISE with both Berkeley (Red waveform) and another simulator (Blue, Green, Pink waveforms). The AFS results were more accurate and finished quicker (7X to 2,000X):

Summary

Switched-capacitor noise can both be calculated and simulated. Transient noise analysis is the preferred analysis type today, especially for larger circuit sizes. Accuracy of noise analysis from the Berkeley AFS tool correlates well with silicon measurements. View the archived webinar here.

More Articles by Daniel Payne …..

lang: en_US

Share this post via:

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center