SPICE circuit simulation is used for transistor-level analysis while Place and Route tools are typically used to connect cells and blocks of an SoC, so why would there be a connection between these two EDA tools?

I read a press release today from ATopTech and Berkeley Design Automation that talked about how SPICE and P&R are connected, so I contacted Eric Thune of ATopTech to learn more. Eric has worked at: Apache Design Solutions, I2 Technologies, Synchronicity, Synopsys and TI.

ATopTech Overview

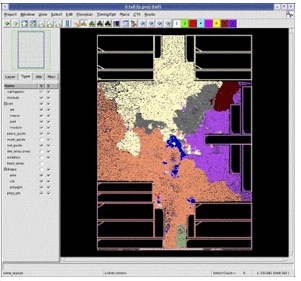

Dr. Ping San Tzeng worked at ArcSys, Avant! and Synopsys reaching the level of Fellow at both Avant! and Synopsys. Starting from scratch they decided to create a hierarchical database and code a P&R engine that could simultaneously optimize for DFM, Timing, Area, voltage islands, and SI using multi-threading and compute farms.

Q&A

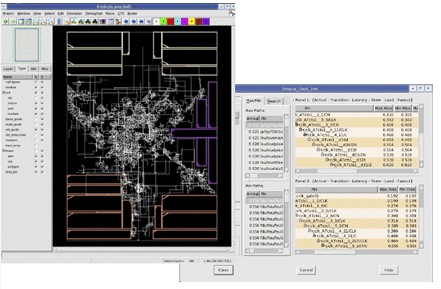

Q: How is the Analog FastSPICE tool from Berkeley DA used with Aprisa?

A: It’s used internally to correlate the results from the timing engine inside our P&R tool Aprisa. Customers running our P&R don’t use the SPICE tool.

Q: What is so different about your approach to P&R?

A: We model the physics correctly and correlate better with sign-off timing tools: Primetime SI, GoldTime (Synopsys), ETS (Cadence).

Q: What’s wrong with other P&R tools?

A: Traditional P&R tools may say that your design will clock at 800MHz, however at signoff it turns out to be only 600MHz.

Q: Do I still need to use a sign-off DRC tool with Aprisa?

A: Yes, although Customers of Aprisa experience clean DRC results that are confirmed by Calibre. Aprisa DRC has to run fast concurrent with P&R, yet stay accurate compared to Calibre.

Q: Why should I choose Aprisa versus Cadence or Synopsys for P&R?

A: In our approach the netlist is never flattened, which is what the other tools do, loosing the hierarchy and intention of designer.

Multiple power domains have been supported from the start with Aprisa, while other P&R vendors have had to bolt this on to their legacy tools (ICC, Encounter).

The hierarchical database makes ECOs take effect quicker in Aprisa.

Q: To correlate your timing accuracy, what SPICE tool were you using before Berkeley AFS?

A: Before BDA we were using another SPICE tool. The reason we choose AFS was: Speed, capacity, accuracy, and a willingness to work together.

Q: How is business for you?

A: ATopTech has been profitable for three years now, and the last time we raised money from VCs was 2005 for $14M. Compare that to Magma using $115M, and Monterey raising $125M in funding.

P&R is about a $600M market segment. Magma got spread too thin. We are staying focused on this single market, big digital. Aprisa is qualified as level 1 for 20nm at TSMC, announced at the same time as other EDA vendors.Q: Do I need to have synthesis and P&R from the same EDA vendor to succeed?

A: No, not really because Synthesis doesn’t understand enough effects of the physical world to make a difference in P&R. We are synthesis agnostic. Our tool can restructure some logic and decompose cells built in.

Q: How long do P&R evaluations take?

A: Evaluations take from 30 day to 6+ months, it’s very dependent on the customer and their designs.

Within a week or so the factory can produce results on customer netlists, where other competitors can take months to respond.

Q: What is the learning curve for Aprisa?

A: Apris is designed to be easy to learn and use, so you don’t need to learn 100’s of switches to get good results quickly. A typical script can be just 60 lines long, versus competitors having 1,000 of lines for the same block.

Q: How is your software sold?

A: It’s sold as Time Based Licenses.

Q: What would success look like 12 months from now?

A: Continuing with a 50% growth rate. Both NA and Asia regions are the growth leaders.

Q: Do I need other EDA tools to complete my P&R job with ATopTech?

A: Customers are using Aprisa for their complete P&R solution, nothing else is required to complete the job.

Q: How does your tool product such quick Turn Around Times?

A: Our tools is multi threaded, and can use compute farms to get the job done quicker. 500K instances to 2M instances are now more common in SoC designs, so quicker TAT is an advantage that we have.

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era