You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 1

[name] => Uncategorized

[slug] => uncategorized

[term_group] => 0

[term_taxonomy_id] => 1

[taxonomy] => category

[description] =>

[parent] => 0

[count] => 186

[filter] => raw

[cat_ID] => 1

[category_count] => 186

[category_description] =>

[cat_name] => Uncategorized

[category_nicename] => uncategorized

[category_parent] => 0

[is_post] =>

)

San Diego Arrival

It’s another picture perfect day in San Diego as I arrived and checked into the Hyatt. The view from the 40th floor looked magnificent, with the Convention Center just a few minutes away in the distance:

Registration

Check in at DAC is quite automated and it took only a minute to receive my official badge with… Read More

In the unspoken war between ARM and Intel, a couple of interesting facts have surfaced during the last few days:

- Intel nervous breakdown in respect with their 30 years old accomplice in the Wintel gang

- ATOM latest version Cedar Trail fabbed on 32nm technology, targeted for mobile computing, will be priced at a 30% to 50% discount…

…

Read More

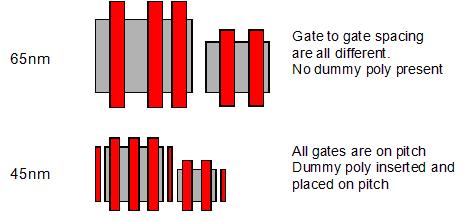

The problem:To move a single lane variable data rate SerDes (serializer-deserializer) from a 65nm process to a 45nm process, achieving a maximum performance of up to 10.3 Gbps. This is a large piece of complex mixed-signal IP with handcrafted analog circuits. Circuit performance and robustness are critical and must be maintained… Read More

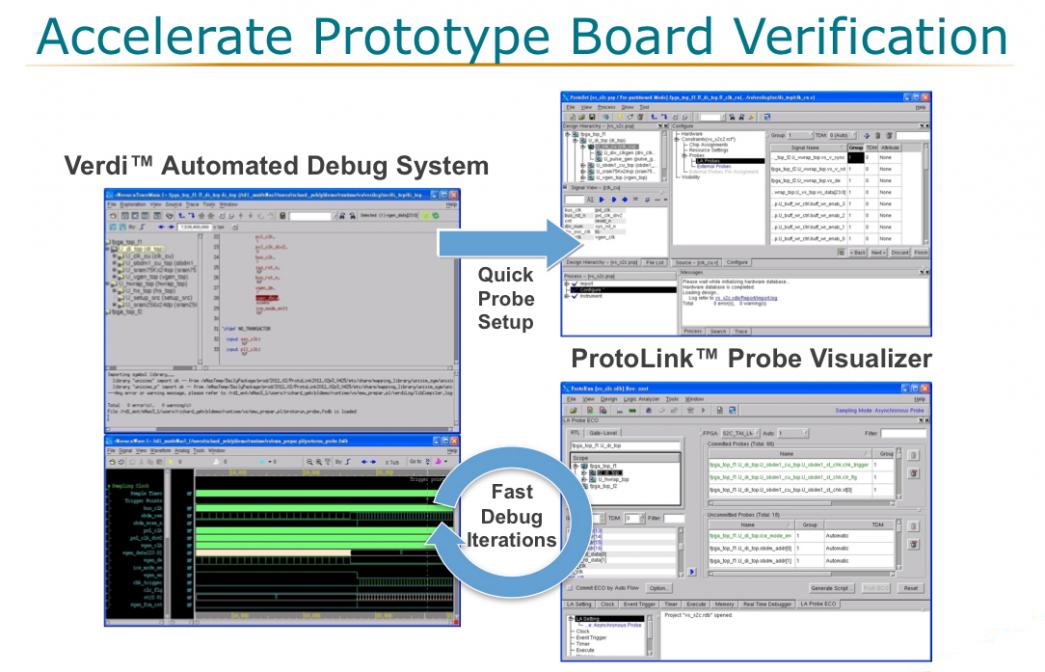

FPGA-based prototype boards are a fast, cost-effective platform for SoC system validation but they are notoriously difficult to set up and to debug. There is a big upside, however, allowing early software integration and testing and thus finding bugs in both the software and the SoC earlier. This approach is much cheaper than … Read More

Concept2Silicon Systems (C2SiS) is focused on providing complete solutions for complex SoC and System designs with best in class engineering capabilities and most cost-efficient business model. Our highly capable engineering team has experience in delivering 200+ silicon and system design solutions to its customers in … Read More

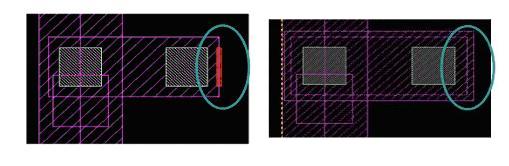

A High-Definition Multimedia Interface (HDMI) IP core was being implemented in an advanced process technology. This fairly large and complex analog mixed-signal (AMS) IP comprising over 130K devices was close to being finalized and shipped to the customer. But many design rules at the foundry were unexpectedly changed from… Read More

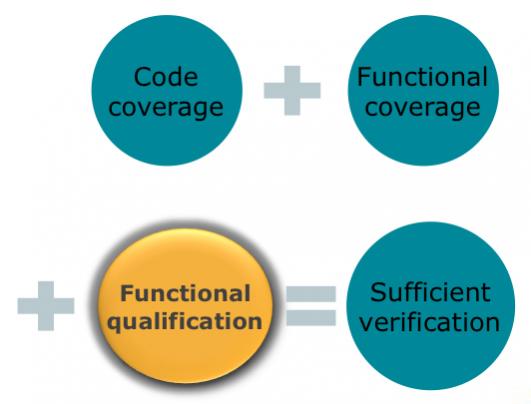

The traditional way for analyzing the effectiveness of testing in the software world and in the RTL world is code coverage. Make sure that every line of code is executed. This is a pretty crude measure since even 100% code coverage doesn’t mean that all the condition has really been tested but it is certainly necessary–after… Read More

The problem:To move dual-port SRAM library and macros from a 40nm process to a 28nm process. In addition to all the changes between two different foundry processes, the 28nm rules are disruptive and incompatible with the previous rules. The memory corecells (foundry-specific) would also need to be completely replaced.

Current… Read More

One of the most demanding areas of layout design has always been memories. Whereas digital design often uses somewhat simplified design rules, memories have to be designed pushing every rule to the limit. Obviously even a tiny improvement in the size of a bit cell multiplies up into significant area savings when there are billions… Read More

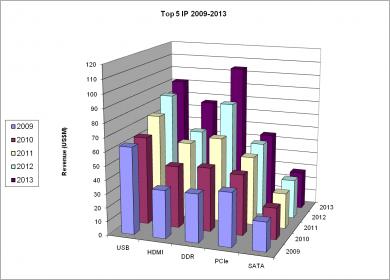

I will share with you some strategic information released by Cadence last week about their IP strategy, more specifically about the launch of the DDR4 Controller IP. And try to understand Cadence strategy about Interface IP in general (USB, PCIe, SATA, DDRn, HDMI, MIPI…) and how Cadence is positioned in respect with their closest… Read More

Things From Intel 10K That Make You Go …. Hmmmm