TSMC announced today that together with ARM they have taped out the first ARM Cortex-A57 64-bit processor on TSMC’s 16nm FinFET technology. The two companies cooperated in the implementation from RTL to tape-out over six months using ARM physical IP, TSMC memory macros, and a commercial 16nm FinFET tool chain enabled by… Read More

Semiconductor Intellectual Property

April 17-19: Overbooked!

For three days in a couple of weeks time there is a crash of conferences, spread out all over the extended Bay Area.

Firstly, from 17-19th April at the Santa Clara Hyatt is the Linley Mobile Conference. This covers all things microprocessor in the mobile industry. Details of the conference including the full agenda are here. The conference… Read More

Apple and Google Turn Towards Enterprise

As a calm settles over the mobile market, post the overhyped Samsung Galaxy S4 launch, many analysts are at a loss as to describe a way forward with Apple that is understandable and positive. The dozens of reports that focus on the summer launches of the iPhone 5S and cheap iphone miss the side of the barn on the true strategy being put… Read More

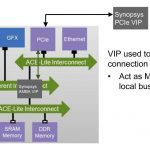

In compliance we trust, for integration we verify

So, you dropped that piece of complex IP you just licensed into an SoC design, and now it is time to fire up the simulator. How do you verify that it actually works in your design? If you didn’t get verification IP (VIP) with the functional IP, it might be a really long day.

Compliance checking something like a PCIe interface block is a … Read More

Simon Segars to be New CEO of ARM

ARM announced today that Warren East, the CEO, would be retiring at the end of June. The new CEO will be Simon Segars, currently President of ARM and the de facto #2 guy. Currently Simon is based in the US and I don’t know if he plans to return to Britain or not. But he will live what will inevitably be a lifestyle that involves crossing… Read More

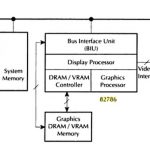

Interconnect Optimization of an SoC Architecture

My last chip design at Intel was a GPU called the 82786and the architects of the chip wrote a virtual prototype using the MAINSAIL language. By using a virtual prototype they were able to:

- Simulate bus traffic, video display and video RAM

- Determine throughput

- Measure latency

- Verify that bus priorities were working

- Optimize the

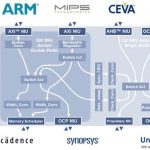

Create Beyond the NoC Solutions!

The Network On Chip (NoC) concept is recent, about 10 years old, and the first implementation of commercially available NoC IP has happened in 2006. Should we drop the concept so quickly after it has been introduced? In fact, I don’t think so… But we could brain storm and imagine the new functions that could be implemented within or… Read More

ARM Cortex SoC Prototyping Platform for Industrial Applications

If your next SoC uses an ARM Cortex-A9 and has an industrial application, then you can save much design and debug time by using a prototyping platform. The price to prototype is quite affordable, and the methodology has a short learning curve. Bill Tomasan Aldec Research Engineer conducted a webinar today on: ARM Cortex SoC Prototyping… Read More

Will next generation Mobile Devices support PCI Express? M-PCIe is coming fast!

Those who have read the numerous articles I have written about MIPI, or PCIe, or the fusion of both named “Mobile Express” know my position: the question is not “Will Mobile devices support PCI Express?” but “When will we see Mobile devices integrating Mobile Express?” I was not really surprised by the Press Release that Cadence … Read More

Cadence To Acquire Tensilica

You have probably already seen the news: Cadence is acquiring Tensilica for $380M. Cadence has been relatively late to the IP party compared to Synopsys. In contrast, Mentor was early, got into the IP business before it was really profitable and ended up shutting down the business.

Tensilica is quite sizable. It has over 200 licensees,… Read More

Breker Hosts an Energetic Panel on Spec-Driven Verification