At the recent Chiplet Summit, presentations, discussions and general participation could be broken down into a few broad categories. There were presentations of actual chiplet designs, either as building blocks or end products. There were presentations regarding design tools and methodologies to support and accelerate … Read More

The Next Hurdle AI Systems Must Clear

AI isn’t having an easy ride. The media and Wall Street swing wildly between extremes on any hint of a shift in AI sentiment. Dickens saw this coming: “It was the best of times, it was the worst of times, it was the age of wisdom, it was the age of foolishness, it was the epoch of belief, it was the epoch of incredulity, it was the season of … Read More

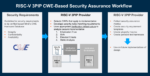

Securing RISC-V Third-Party IP: Enabling Comprehensive CWE-Based Assurance Across the Design Supply Chain

by Jagadish Nayak

RISC-V adoption continues to accelerate across commercial and government microelectronics programs. Whether open-source or commercially licensed, most RISC-V processor cores are integrated as third-party IP (3PIP), potentially introducing supply chain security challenges that demand structured,… Read More

Arteris Smart NoC Automation: Accelerating AI-Ready SoC Design in the Era of Chiplets

As semiconductor design pushes into increasingly complex territory, driven by Ai, ML, HPC, and heterogeneous system architectures, designers are challenged to balance performance, power, and time-to-market pressures. In this landscape, network-on-chip (NoC) architectures have emerged as a foundational building block… Read More

WEBINAR: Why Network-on-Chip (NoC) Has Become the Cornerstone of AI-Optimized SoCs

By Andy Nightingale, VP of Product Management and Marketing

As AI adoption accelerates across markets, including automotive ADAS, large-scale compute, multimedia, and edge intelligence, the foundations of system-on-chip (SoC) designs are being pushed harder than ever. Modern AI engines generate tightly coordinated, … Read More

The IO Hub: An Emerging Pattern for System Connectivity in Chiplet-Based Designs

In chiplet-based design we continue the march of Moore’s Law by scaling what we can put in a semiconductor package beyond the boundaries of what we can build on a single die. This style is already gaining traction in AI applications, high performance computing, and automotive, each of which aims to scale out to highly integrated … Read More

Arteris Simplifies Design Reuse with Magillem Packaging

Many know Arteris as the “network-on-chip”, or NoC, company. Through acquisitions and forward-looking development, the footprint for Arteris has grown beyond smart interconnect IP. At DAC this year, Arteris highlighted its latest expansion with a new SoC integration automation product called Magillem Packaging. The announcement… Read More

Arteris at the 2025 Design Automation Conference #62DAC

Key Takeaways:

- Expanded Multi-Die Solution: Arteris showcases its foundational technology for rapid chiplet-based innovation. Check out the multi-die highlights video.

- Ecosystem compatibility: Supported through integration with products from major EDA and foundry partners, including Cadence, Synopsys, and global

Arteris Expands Their Multi-Die Support

I am tracking the shift to multi-die design, so it’s good to see Arteris extend their NoC expertise, connecting chiplets across an interposer. After all, network connectivity needs don’t stop at the boundaries of chiplets. A multi-die package is at a logical level just a scaled-up SoC for which you still need traffic routing and… Read More

How Arteris is Revolutionizing SoC Design with Smart NoC IP

Recently, Design & Reuse held its IP-SoC Days event at the Hyatt Regency in Santa Clara. Advanced IP drives a lot of the innovation we are seeing in chip design. This event provides a venue for IP providers to highlight the latest products and services and share a vision of the future. IP consumers are anxious to hear about all the… Read More