The analysts at Gary Smith EDA produce an annual What To See List for DAC and I quickly noticed that all three major EDA vendors were included on the list for the specific category of emulation. The big problem that emulation addresses is the ability to run in hardware an early version of your SoC so that software developers can get access… Read More

High Density Advanced Packaging Trends

Thursdays at the Design Automation Conference (DAC) are always a good time to catch up on areas of technology which are adjacent to that which you normally work. The exhibit floor is over and you have more time to spend in seminars. At this year’s DAC, I took advantage of a half day seminar put on by Mentor, a Siemens business, … Read More

HLS update from Mentor about Catapult

I recall back in the late 1980’s when logic synthesis tools were first commercialized, at first they could read in a gate-level netlist from one foundry then output an optimized netlist back into the same foundry. Next, they could migrate your gate-level netlist from Vendor A over to Vendor B, giving design companies some… Read More

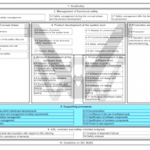

Rob Bates on Safety and ISO26262

Most of us would agree that safety is important in transportation and most of us know that in automotive electronics this means ISO26262 compliance. But, except for the experts, the details don’t make for an especially gripping read. I thought it would be interesting to get behind the process to better understand the motivation,… Read More

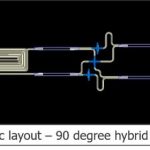

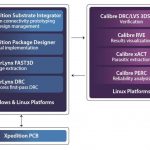

Mentor & Phoenix Software Shed Light on Integrated Photonics Design Rule Checking

Just prior to the opening of the 54[SUP]th[/SUP] Design Automation Conference, Mentor, a Siemens company, and PhoeniX Software issued a press release announcing a new integration between their tools to help designers of photonic ICs (PICs) to close the loop for manufacturing sign-off verification. This is a significant piece… Read More

Overcoming the Challenges of Creating Custom SoCs for IoT

As the Internet of Things (IoT) opportunities continues to expand, companies are working hard to bring System-on-Chip (SoC) solutions to market in the hopes of garnering market share and revenue. However, it’s not as easy as it may first seem. Companies are running into a series of issues that stand between them and capturing the… Read More

The Real Reason Siemens Bought Mentor!

The Siemens purchase of Mentor last year for a premium $4.5B was a bit of a shock to me as I have stated before. I had an inkling a Mentor acquisition was coming but Siemens was not on my list of suitors. The reviews have been mixed and the Siemens commitment to the IC EDA market has been questioned so I spent some time on this at #54DAC.

First… Read More

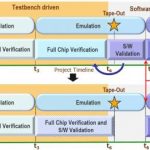

Listening to Veloce Customers: Emulation is Thriving

We have seen methodology shifts in our industry; emulation is going through a fundamental shift in usage, scope of the tasks, deployment, enterprise level and vertical market focus.… Read More

Tools for Advanced Packaging Design Follow Moore’s Law, Too!

There is an emerging set of advanced packaging technologies that enables unique product designs, with the capability to integrate multiple die, from potentially heterogeneous technologies. These “system-in-package” (SiP) offerings provide architects with the opportunity to optimize product performance, power, cost,… Read More

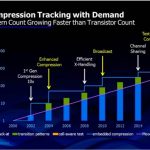

Time is Money, Especially when Testing ICs

Semiconductor companies are looking for ways to keep their business profitable by managing expenses on both the design and test side of electronic products, which is quite the challenge as the trends show increases in test pattern count and therefore test costs. Scan compression is a well-known technique first created over 15… Read More