Design process retargeting is acommon recurrence based on scaling orBOM(Bill-Of-Material) cost improvement needs. This occursnot only with the availability of foundry process refresh to a more advanced node,but also to any new derivative process node tailored towards matching design complexity, power profile or reliability… Read More

Concluding Inconclusives

Formal methods are a vital complement to other tools in the verification arsenal, but they’re not without challenges. One of the more daunting is the “inconclusive” result – that case where the tool seems to be telling you that it simply gave up trying to figure out if a particular assertion is true or false. Compounding the problem,… Read More

Developing Affordable IoT Systems

The IoT market opportunities in segments like wearables, vehicles, home, cities and industrial are all growing thanks to the combination of semiconductors, sensors, software and systems technology. New hardware designs for IoT edge devices appear on a daily basis, and the companies behind these new products can often be start-ups… Read More

Mentor Tessent MissionMode Provides Runtime DFT for Self-Correcting Automotive ICs

The automotive industry continues push the limits on how “smart” we can make our vehicles and from that, it follows as to how smart we can make the electronics in the vehicles. When I think of smart cars (and smart automotive ICs) I typically think of things like advanced driver-assistance systems (ADAS) that use AI and neural networks… Read More

SPIE 2018 Mentor Graphics Scott Jones and SemiWiki

Next week is SPIE, the leading lithography networking event here in Silicon Valley. Scott Jones is not only attending but also presenting at the 15th Annual LithoVision on Sunday. I will be at SPIE as well so if you want to meet up let us know. We will publish a blog on Scott’s presentation the morning of for those who cannot attend.… Read More

DVCon 2018 Mentor Graphics and SemiWiki

DVCon turns 30 this year which is a very big deal. My oldest child also turns 30 this year which really puts things in perspective looking back at what we have all accomplished during that time. DVCon originally started as a user’s group at the 1988 Design Automation Conference in Anaheim California and the rest as they say is history.… Read More

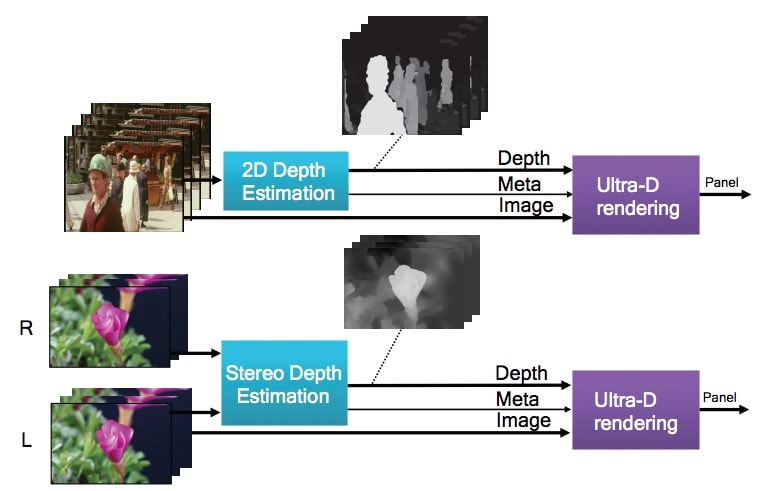

Designing an SoC for 3D TV Without using the Funny Glasses

In the blur of activities at DAC last year I visited the Mentor booth a few times and had just a few minutes to glance at a 3D TV display that didn’t require me to wear any funny glasses, kind of novel I thought at the time because I’ve read that the market of 3D TV sets is being hampered by requiring viewers to wear glasses. The… Read More

A Reliable Way to Forecast Growth of Semiconductor Markets

Wally Rhines, President and CEO of Mentor, a Siemens Group, did another one of his famous deep learning presentations at SEMI ISS 2018. Using the Gompertz Curve Lifecycle to forecast the future growth of semiconductor markets, Wally looks at: Image sensors, Desktop PCs, PC Notebooks, Cell Phone Subscribers, Smartphones, and… Read More

Mentor Tessent Products Ready for Second Edition of ISO 26262 Coming in March 2018

Have you notice how smart your automobile is getting? Watching the first round of NFL playoffs I lost count on the number of TV commercials showing cars weaving through tight construction zones (and Star Wars figures), big trucks parking in incredibly tight spaces, cars avoiding rear-end collisions and pedestrians, and even … Read More

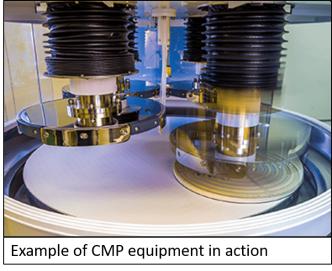

Mentor Investigates Using Neural Networks for CMP Modeling

I recently read a new white paper release by Mentor, a Siemens Business, that delved into the intricacies of Chemical Mechanical Polishing (CMP) and I got a sense of Déjà vu. My professional career in the IC industry started at Texas instruments and the white paper made me think of a conversation I had with one of my colleagues over … Read More