Having spent my entire thirty plus year career in semiconductors and design enablement I have seen quite a change in diversity. When I first started I remember thinking that height and weight was the only diversity here in Silicon Valley. My wife really noticed it when she attended her first Design Automation Conference in 1985 … Read More

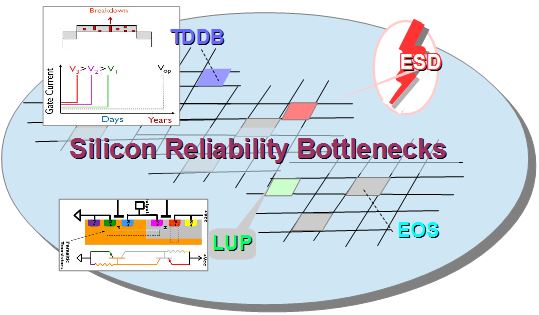

Electrical Reliability Verification – Now At FullChip

Advanced process technology offers both device and interconnect scaling for increased design density and higher performance while invoking also significant implementation complexities. Aside from the performance, power and area (PPA) aspects, designer is getting entrenched with the need of tackling more reliability … Read More

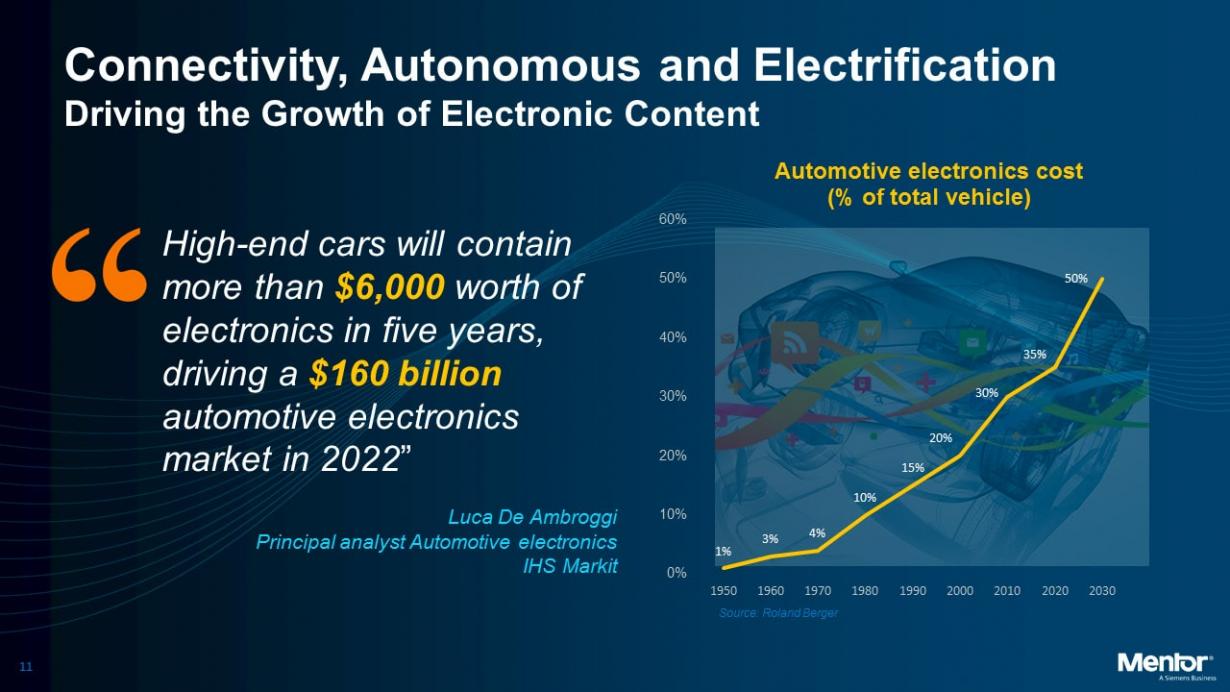

Mentor’s Approach to Automotive Electrical Design

Most of us continue to drive cars and for me there’s always been a fascination with all things electrical that go into the actual design of a car. I’ve done typical maintenance tasks on my cars over the years like changing the battery, installing a new radio, replacing bulbs, changing a fuse, swapping out dashboard lights,… Read More

EDA CEO Outlook 2018 Partly Cloudy

The funniest line of the EDA CEO Outlook event was that we should rename our Amazon Echos Wally. Yes Wally is that smart and he remembers pretty much everything. I wish I could rename my Echo Wally because my daughter in-law is named Alexa so we have to turn it off when she is over. The discussion took an interesting turn with EDA in the … Read More

Mentor Leads Emulation Innovation

Publishing eBooks on FPGA Prototyping and Emulation really was an eye opener for me as a long time EDA and IP professional. Both markets are considered EDA in the traditional sense but they are very much in the systems business with a lot of IP. Both markets are also growing very rapidly and operate side-by-side with complimentary… Read More

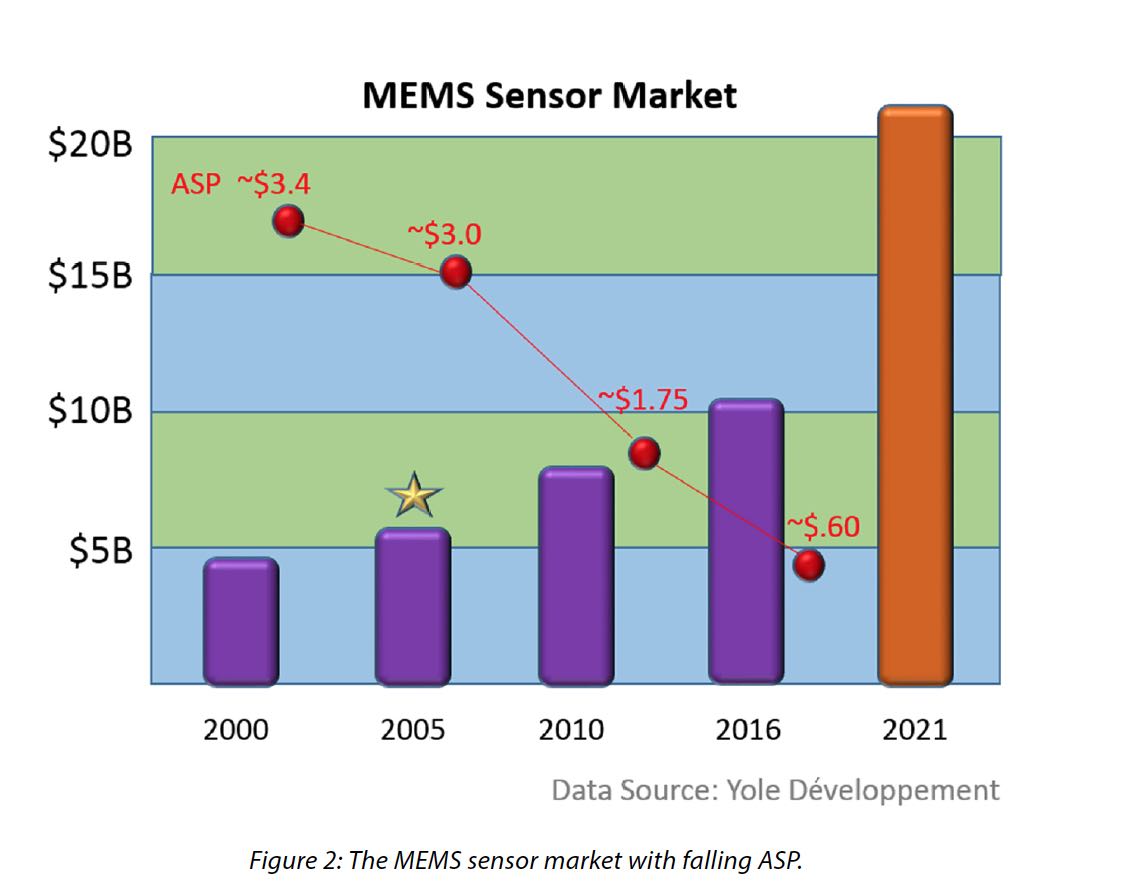

Edge Devices Rely on Intelligent MEMS Based Sensors

MEMS sensors play a huge role in intelligent systems these days. Mobile and IoT devices would essentially be blind if not for the rich variety of MEMS sensors integrated into them. The MEMS sensor market is growing rapidly, topping $10B in 2016 and slated to exceed $20B by 2020. MEMS is also growing in the RF market, where they are providing… Read More

Siemens Leverages Mentor Embedded IoT Framework for Industry 4.0

For those of you who wondered at the logic behind Siemens acquisition of Mentor Graphics last year, look no further than a recent announcement by Mentor, now a Siemens business, regarding the release of their new Mentor Embedded IoT Framework (MEIF). To help connect the dots, we need to back up a bit and review a few things about how… Read More

Don’t Stand Between The Anonymous Bug and Tape-Out (Part 2 of 2)

The second panel is about system coverage and big data. Coverage metrics have been used to gauge the quality of verification efforts during development. At system level, there are still no standardized metrics to measure full coverage. The emergence of PSS, better formal verification, enhanced emulation and prototyping techniques… Read More

Computer Vision and High-Level Synthesis

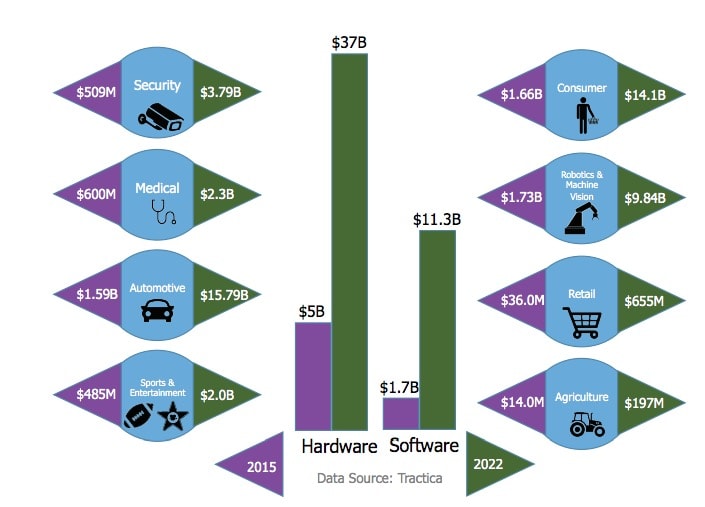

Computer vision as a research topic has been around since the 1960’s and we are enjoying the benefits of this work in modern-day products all around us as robots with computer vision are performing an increasing number of tasks, even our farmers are using computer vision systems to become more productive:

- AgEagle® has a drone

EDA and Semiconductor — Is There Growth In The Ecosystem?

The semiconductor industry has gone through several major transitions driven by different dynamics such as shift in business models (fab-centric to fab-less), product segmentation (system design house, IP developers) and end market applications (PC to cloud; and recently, to both automotive and Internet of Things — IOT’s,… Read More