You don’t often hear about the inner workings of EDA tools and flows – the marketing guys much prefer telling us about all the exciting things their tools can do rather than the internal plumbing. But this matters for making design flows – and building these has largely been left to the users to sort out. That’s an increasing challenge… Read More

An Update on HLS and HLV

I first heard about High Level Synthesis (HLS) while working in EDA at Viewlogic back in the 1990s, and have kept watch on the trends over the past decades. Earlier this year Siemens EDA hosted a two day event, having speakers from well-known companies share their experiences about using HLS and High Level Verification (HLV) in their… Read More

Cracking post-route Compliance Checking for High-Speed Serial Links with HyperLynx

SemiWiki readers from a digital IC background might find it surprising that post-PCB route analysis for high speed serial links isn’t a routine and fully automated part of the board design process. For us, the difference between pre- and post-route verification is running a slightly more accurate extraction and adding SI modelling,… Read More

Calibre: Early Design LVS and ERC Checking gets Interesting

The last thing you want when taping out a design is to hit large numbers of violations in signoff checks that could have been flushed out and resolved in earlier flow iterations. For implementation flows (floorplanning, synthesis, place and route), it’s usual to do a lot of flow flushing work early in the design cycle and iteratively… Read More

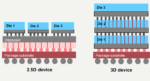

Architectural Planning of 3D IC

Before chiplets arrived, it seemed like designing an electronic system was a bit simpler, as a system on chip (SoC) methodology was well understood, and each SoC was mounted inside a package, then the packages for each component were interconnected on a printed circuit board (PCB). The emerging trend to design a 3D IC using chiplets… Read More

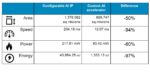

Pushing Acceleration to the Edge

As more AI applications turn to edge computing to reduce latencies, the need for more computational performance at the edge continues to increase. However, commodity compute engines don’t have enough compute power or are too power-hungry to meet the needs of edge systems. Thus, when designing AI accelerators for the edge, Joe… Read More

Why Use PADS Professional Premium for Electronic Design

My IC design career started just a few years before PADS got started in 1985 with a DOS-based tool for PCB design. A lot has changed since then, as PADS was acquired by Mentor Graphics in 2001, and continued to grow under Siemens EDA, now with four versions to choose from, where the top version is called PADS Professional Premium:

- PADS

DFT Moves up to 2.5D and 3D IC

The annual ITC event was held the last week of September, and I kept reading all of the news highlights from the EDA vendors, as the time spent on the tester can be a major cost and the value to catching defective chips from reaching production is so critical. Chiplets, 2.5D and 3D IC design have caught the attention of the test world, … Read More

Siemens EDA Discuss Permanent and Transient Faults

This is a topic worth coverage for those of us who aim to know more about safety. There are devils in the details on how ISO 26262 quantifies fault metrics, where I consider my understanding probably similar to other non-experts: light. All in all, a nice summary of the topic.

Permanent and transient faults 101

The authors kick off … Read More

3D IC – Managing the System-level Netlist

I just did a Google search for “3D IC”, and was stunned to see it return a whopping 476,000 results. This topic is trending, because more companies are using advanced IC packaging to meet their requirements, and yet the engineers doing the 3D IC design have new challenges to overcome. One of those challenges is creating… Read More