SemiWiki readers from a digital IC background might find it surprising that post-PCB route analysis for high speed serial links isn’t a routine and fully automated part of the board design process. For us, the difference between pre- and post-route verification is running a slightly more accurate extraction and adding SI modelling,… Read More

Electronic Design Automation

Synopsys Crosses $5 Billion Milestone!

“We intend to grow revenue 14% to 15%, continue to drive notable ops margin expansion and aim for approximately 16% non-GAAP earnings per share growth.”

Synopsys, Inc. (NASDAQ:SNPS) Q4 2022 Earnings Call Transcript

Synopsys is the EDA bellwether since they report early and are the #1 EDA and #1 IP company. In addition to crossing… Read More

Bizarre results for P2P resistance and current density (100x off) in on-chip ESD network simulations – why?

Resistance checks between ESD diode cells and pads or power clamps, and current density analysis for such current flows are commonly used for ESD networks verification [1]. When such simulations use standard post-layout netlists generated by parasitic extraction tools, the calculated resistances may be dramatically higher… Read More

Solutions for Defense Electronics Supply Chain Challenges

“The amateurs discuss tactics: the professionals discuss logistics.”

— Napoleon

Logistics is even more important today than it was in the early 1800’s. Further, the effectiveness of Defense systems is increasingly driven by sophisticated electronics. As the recent Ukraine conflict reveals, weapons such as precision munitions,… Read More

Live Webinar: Code Review for System Architects

Register management tools have been used mostly in a bottom-up approach. There are some documents and/or spreadsheets created by the System Architects that are delivered to the design and verification teams. They then start capturing the HW/SW interface of the peripheral IPs in their in-house or commercial register management… Read More

INNOVA PDM, a New Era for Planning and Tracking Chip Design Resources is Born

No doubt that the design success of nowadays system on chips (SoCs) is directly linked to the success of cost control. More market opportunities are open for less expensive system on chips and electronic systems.

Both the design cost prediction and the resource tracking during the design process, are key to such a success

Predicting… Read More

IDEAS Online Technical Conference Features Intel, Qualcomm, Nvidia, IBM, Samsung, and More Discussing Chip Design Experiences

Ansys is hosting IDEAS Digital Forum 2022, a no-cost virtual event that brings together industry executives and technical design experts to discuss the latest in EDA for Semiconductors, Electronics, and Photonics.

See the full online conference agenda and list of speakers at www.ansys.com/IDEAS. The free registration will… Read More

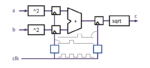

The Role of Clock Gating

Perhaps you’ve heard the term “clock gating” and you’re wondering how it works, or maybe you know what clock gating is and you’re wondering how to best implement it. Either way, this post is for you.

Why Power Matters

I can’t help but laugh when I watch a movie where the main characters are shrunk… Read More

Ant Colony Optimization. Innovation in Verification

Looking for better ways to search a huge state space in model checking, Ant Colony Optimization (ACO) is one possible approach. Paul Cunningham (Senior VP/GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and now Silvaco CTO) and I continue our series on research ideas. As always,… Read More

A Crash Course in the Future of Technology

One of the harshest lessons we learned during the recent pandemic is the power of exponentials. As human beings, we are linear thinkers and can’t fathom how doublings of viruses — or technologies — can be destructive and disrupt everything. In my university classes and talks to business executives, I have always had to explain… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center