The meaning of the word “Veloce” is “blazing fast”. It is the inspiration behind the name of the Ansys VeloceRF electromagnetic (EM) passive device synthesis platform that has been a favorite among RF and high-speed integrated circuit (IC) designers for more than 15 years. VeloceRF is a name that designers automatically connect… Read More

Electronic Design Automation

Synopsys is Paving the Way for Success with 112G SerDes and Beyond

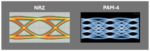

Data communication speeds continue to grow. New encoding schemes, such as PAM-4 are helping achieve faster throughput. Compared to the traditional NRZ scheme, PAM4 can send twice the signal by using four levels vs. the two used in NRZ. The diagram at the top of this post shows the how data density is increased. With progress comes… Read More

Rigid-flex PCB Design Challenges

From Zion Research I learned that the flexible electronics market was about $13.2B in 2021 and growing at a CAGR of 21%, so that was impressive. There are several factors that make rigid-flex circuit so attractive, like: space efficiency, reduced weight, enhanced reliability, improved signal integrity, streamlined assembly,… Read More

Accelerate SoC Design: DIY, FPGA Boards & Commercial Prototyping Solutions (I)

In the early days, chip designers had to rely on time-consuming simulation results or wait for the engineering sample to validate whether the design meets its intended objectives. With the increasing complexity of SoC designs, the need to accelerate software development has also risen to ensure a timely entry to market.

In the… Read More

Podcast EP221: The Importance of Design Robustness with Mayukh Bhattacharya

Dan is joined by Mayukh Bhattacharya, Engineering, Executive Director, at Synopsys. Mayukh has been with Synopsys since 2003. For the first 14 years, he made many technical contributions to PrimeSim XA. Currently, he leads R&D teams for PrimeSim Design Robustness and PrimeSim Custom Fault products. He was one of the early… Read More

Self-heating and trapping enhancements in GaN HEMT models

High-fidelity models incorporating real-world, cross-domain effects are essential for accurate RF system simulation. The surging popularity of gallium nitride (GaN) technology in 5G base stations, satellite communication, defense systems, and other applications raises the bar for transistor modeling. Keysight dives… Read More

Anirudh Keynote at CadenceLIVE 2024. Big Advances, Big Goals

The great things about CEO keynotes, at least from larger companies, is that you not only learn about recent advances but you also get a sense of the underlying algorithm for growth. Particularly reinforced when followed by discussions with high profile partner CEOs on their directions and areas of common interest. I saw this recently… Read More

Will my High-Speed Serial Link Work?

PCB designers can perform pre-route simulations, follow layout and routing rules, hope for the best from their prototype fab, and yet design errors cause respins which delays the project schedule. Just because post-route analysis is time consuming doesn’t mean that it should be avoided. Serial links are found in many PCB designs,… Read More

Enabling Imagination: Siemens’ Integrated Approach to System Design

In today’s rapidly advancing technological landscape, semiconductors are at the heart of innovation across diverse industries such as automotive, healthcare, telecommunications, and consumer electronics. As a leader in technology and engineering, Siemens plays a pivotal role in empowering the next generation … Read More

Design Stage Verification Gives a Boost for IP Designers

The concept of shift left is getting to be quite well-known. The strategy involves integrating various checks typically performed later in the design process into earlier stages. The main benefit is to catch and correct defects or errors at an earlier stage when it’s easier and faster to address. For complex SoC design, … Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry