You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4380

[filter] => raw

[cat_ID] => 157

[category_count] => 4380

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

Digital hardware has a habit of deciding – based on the bias and behavior of transistors – to drive outputs to a 0, or a 1, or if commanded a high-impedance Z state. SystemVerilog recognizes a fourth state: X, the “unknown” state a simulator has trouble inferring.

Simulators have a choice. Under X-optimism, they can convert the unknown… Read More

The first part of Lars Liebmann’s ICCAD keynote about lithography was on the changes in lithography that have to us to where we are today. In some ways it was an explanation of why we have the odd design rules, double patterning etc that we have in 20nm and 16nm processes. The second part of his talk was a look forward to how we might… Read More

There is always a lot of posturing and pontificating when semiconductor executives talk about the future of process development. They are fighting an air war of perception and investor expectations, so naturally want to make sure they have plenty to brag about. But, as we pointed out recently with Intel’s problems at 14nm, moving… Read More

Save closure time and boost performance by incorporating knowledge of physically aware design early into your front-end design implementation flow

With the adoption of advanced process nodes, design closure is becoming increasingly difficult due to the lack of convergence between the front end and the back end of the register-transfer… Read More

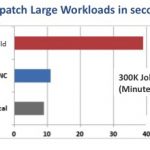

When you see a new product announcement from an EDA company, it is always put in terms that make it seem as if the engineer is sitting at his or her desktop with a big server and is running the new tool to wondrous effect. But the reality in the real world is that most companies have a computing infrastructure of server farms, often several… Read More

Yesterday Cadence had an all-day Signoff Summit where they talked about the tools that they have for signoff in advanced nodes. Well, of course, those tools work just fine in non-advanced nodes too, but at 20nm and 16nm there are FinFETs, double patterning, timing impacts from dummy metal fill, a gazillion corners to be analyzed… Read More

The first time that I saw a DRAM in a ceramic package running on a tester I made the mistake of touching my finger to the metal lid, scorching my finger and teaching me a lesson that ICs can run extremely hot. I’ve read a lot the past few years about 3D IC design, and immediately my mind becomes curious about how an engineer would go… Read More

At major EDA events, CEDA (the IEEE council on EDA, I guess you already know what that bit stands for) hosts a lunch and presentation for attendees and others. This week was ICCAD and the speaker was Lars Liebmann of IBM on The Escalating Design Impact of Resolution-Challenged Lithography. Lars decided to give us a whirlwind tour … Read More

The Internet of Things is on every technology mind these days, but what does it mean for the EDA community? Dennis Brophy of Mentor Graphics says the billions of things we are hearing about will not happen unless we find a way to build a lot more things, efficient things, and connected things. He has more thoughts in our recent interview.… Read More

Connecting “things” to the Internet and enabling sensing and remote control, data gathering, transmission, and analysis improves many areas: safety and quality of life, healthcare, manufacturing and service delivery, energy efficiency, and the environment. The concept of the Internet of Things (IoT) is quickly becoming… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center